用过DSP_Builder工具的朋友一定用过Delay模块,这个可是算法设计中必须用到的东西,它能让你的数据延时几个时钟再出现,那么在这个模块同一个Library中你是否注意到还有一个Memory Delay模块。咋一看,这两个模块貌似是一样的,因为都有Delay,不过再一想,既然分开存放,那肯定又有所不同。下面,跟随着笔者带你看看究竟这里面藏着什么秘密。

首先,我们来看一个实验,这个实验如下图所示。

我们对这个算法进行编译,目的是查看这两个不同的Delay模块综合成了什么样的电路以及消耗的资源情况怎样。

对上图资源使用情况,我们只关心两个地方就足够了,一个是Logic Cells,一个是M4Ks。Logic Cells是FPGA内部的逻辑单元,我们生成电路主要靠的就是它了;M4Ks是Altera低端FPGA配备的内部RAM资源,4K的意思就是它的容量是4K bits(注意这儿单位是位)。由这里可以看出Delay1模块消耗了8个Logic Cells,Memory Delay也消耗了8个Logic Cells。忙活了半天,原来这两个模块消耗的资源是一样的,我们再来看一下综合的电路吧。

看了上图发现,这两个模块综合成的电路都是一样的。笔者坚信,这两个模块肯定有所不同,那能不能通过综合优化选项改变综合后的电路呢,笔者更改了Analysis & Synthesis Settings下的Optimization Technique。

不论采用Speed、Balanced还是Area,效果都是一样的。笔者又试验了两个时钟单位的延时,两个模块综合出来还是完全一样。

功夫不负有心人,当我把延时值增加到3时,就出现了不同效果了。

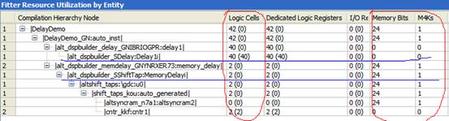

下图是延时3个时钟时的资源消耗情况。

看到这个图,我们终于可以高兴一下了,因为我们找出了它们的不同,Delay1消耗了24个Logic Cells,没有用到M4Ks;而Memory Delay消耗了5个Logic Cells,同时消耗了1个M4Ks。这里就好理解为什么叫Memory Delay了吧,因为它需要占用FPGA的RAM资源;而Delay模块不占用RAM资源,而是消耗Logic Cells资源,那究竟是不是这样呢,让我接下来一探究竟吧。既然资源消耗不同,那综合出的电路也不同了,这里感兴趣的朋友可以自己试验一下。

笔者还没有放弃,继续试验,试图彻底了解它们俩兄弟。笔者又进行了4时钟延时的试验,结果这次更复杂了,先看看4时钟延时的资源消耗情况吧。

对比上面两幅图,笔者惊讶的发现,我进行4个Memory Delay的延时,结果比进行3个Memory Delay的延时,消耗的资源还要少,这里确实有些复杂。当我们看RAM Summary时发现,3个延时时生成的RAM是双时钟的简单双口RAM,而4个延时时声称的RAM是单时钟的简单双口RAM,这就是答案所在,究竟Altera为什么要那么做,笔者也不清楚。

当我把延时值进一步加到5时,更为奇特的事情发生了,且听笔者慢慢道来。下图是我在用Speed模式优化综合器时生成电路的资源消耗情况。

Delay1模块消耗了40个Logic Cells,这里好理解,8位输入输出,每个延时消耗8个Logic Cells,一共40个。但是,Memory Bits为什么只有24 bits,按道理应该是40 bits才对啊。当我们观察生成的电路结构时会发现,M4K每个块输入输出口都配备有一个D触发器,这个触发器可以选择使用不使用,而每个D触发器都相当于一个延时,这样就好理解为什么是24 bits了吧。

而当我们用Balance或者Area选项去优化综合器时,又出现了不同的效果,且看下图。

看到了吧,Delay1消耗了8个Logic Cells和16 bits M4K,而Memory Delay消耗了24 bits M4K,貌似越来越复杂了。其实当我们看了综合成的电路后就感觉不到复杂了,Delay在利用Memory延时之前先进行了1个延时,即8个Logic Cells用作了1个时钟的延时,究竟为什么这样,也只有Altera的工程师能说清楚了。

接下来,相信大家都会像笔者一样,有接着往下做实验的冲动。有兴趣大家可以多试验几种情况,在这里给出大家一个结论,当所设定的延时值*数据位宽小于逻辑单元数量时,综合出来的结论都和5个延时值时相同;而当延时值*数据位宽大于逻辑单元数量时,用Speed优化选项编译会报错,而用Balance或Area优化选项编译时正常。

通过上面的实验,我对我们已经对Delay和Memory Delay有个清楚的认识了,但我们找出这些区别并是不完全出于兴趣,下一篇博文将会进一步说明我们怎么利用这些不同设计自己的算法,以节省FPGA资源。

/2

/2

文章评论(0条评论)

登录后参与讨论