把这篇文章分享出来给大家,把我这过程中遇到的问题以及解决问题的办法罗列出来,希望做这个实验的看到我的这篇文章能够少走一些弯路,虽然我写的很“通俗”,可能文章中还会有错误,但是这不是一个学习的过程吗?希望有高手能够找出我的错误,希望我们一起进步。我使用的Spantan-3E,xilinx公司的一块入门实验板,包括50万门,XC3S500E-4FG320C的FPGA芯片,下面是开发板中的一些资料,也许一些人会有很少的一段时间就能看明白,但是我却看了很久,才懂得。

入门实验板通过DB15连接器输出一个VGA显示端口。该端口通过标准的监视电缆直接连到PC监视器或平板LCD上。如图6.1所示,VGA连接器在板上的最左端。

FPGA通过串联电阻直接驱动5个VGA信号。每个颜色信号串一个电阻,每位的颜色信号分别是VGA_RED、VGA_BLUE、VGA_GREEN。每个电阻与终端的75欧电缆电阻相结合,确保颜色信号保持在VGA规定的0V~0.7V之间。VGA_HSYNC和VGA_VSYNC信号使用LVTTL或LVCMOS3I/O标准驱动电平。通过VGA_RED、VGA_BLUE、VGA_GREEN置高或低来产生8中颜色,如表6.1所示。

VGA信号的时序由视频电气标准委员会(VESA)规定。以下提供的VGA系统和时序信息作为例子来说明FPGA在640×480模式下是如何驱动VGA监视器的。

Signal Timing for a 60 Hz, 640x480 VGA Display

VGA显示器基于CRT,使用调幅模式,移动电子束(或阴极射线)在荧光屏上显示信息。LCD使用矩阵开关给液晶加压,在每个像素点上通过液晶来改变光的介电常数。尽管下面的描述仅限于CRT,LCD已经发展到可以同CRT使用同样的时序信号了。因此,下面的讨论均适合CRT和LCD。

在CRT显示器中,电流的波形通过蹄形磁铁产生磁场,使得电子束偏转,光栅在显示屏上横向显示,水平方向从左至右,垂直方向从上至下。如图6.2所示,当电子束向正方向移动时,信息才显示,即从左至右、从上至下。如果电子束从后返回左或顶边,显示屏并不显示任何信息。在消隐周期——电子束重新分配和稳定于新的水平或垂直位时,丢失了许多信息。

显示协议定义了电子束的大小以及通过显示屏的频率,该频率是可调的。

现在的VGA显示屏支持多种显示协议,VGA控制器通过协议产生时序信号来控制光栅。控制器产生同步脉冲TTL电平来设置电流通过偏转磁铁的频率,以确保像素或视频数据在适当的时间送给电子*。

视频数据一般来自重复显示存储器中一个或多个字节——它们被分配到每个像素单元。入门实验板使用每个像素中的3位,产生表6.1中可能的一种颜色。控制器指定视频数据缓冲器以备电子束通过显示屏。然后,控制器接收并利用视频数据在适当的时间显示,电子束移动到指定的像素点。

根据图6.2所示,VGA控制器产生水平同步时序信号(HS)和垂直同步时序信号(VS),调节在每个像素时钟视频数据的传送。像素时钟定义了显示像素信息的有效时间段。VS信号定义显示的更新频率,或刷新屏幕信息的频率。最小的刷新频率是取决于显示器的亮度和电子束的强度,实际频率一般在60~120Hz之间。给定的刷新频率的水平线的数量定义了水平折回频率。

VGA Signal Timing

表6.2的时序信号是640×480,像素时钟25Mhz,刷新频率60Hz±1。图6.3说明了每个时序的联系。同步脉冲的时序宽度(TPW)和前后门拱的间隔TFP和TBP)基于观察多种VGA的显示屏的结果。前后门拱的间隔是前后同步脉冲时间。在这些时段信息不能显示。

一般来说,时钟计数器通过像素时钟来控制水平时序信号。译码计数器的值产生HS信号。在指定的行,计数器产生当前像素显示的位置。

一个独立的计数器产生垂直时序信号。垂直同步计数器在每个HS脉冲信号来临时自动加1,译码值产生VS信号。计数器产生当前显示行。这两个计数器从地址到显示缓冲器连续计数。例如,入门实验板的DDR SDRAM 提供了一个足够的显示缓冲区。

在HS脉冲的开始和VS脉冲的开始没有具体规定相对的时序关系。因此,计数器被分配到简单格式的视频RAM地址,或分配到同步脉冲产生器的最小译码逻辑。

UCF Location Constraints

图6.4提供了VGA显示端口的UCF约束,包括I/O口管脚分配和I/O口使用标准,输出摆率和输出驱动电流。

现在回头看看其实资料已经非常详细了,只不过自己的理解能力有限,浪费了许多不需要浪费的时间,可能这是每个人都需要经过的阶段吧,说一下在做这儿实验的过程中自己遇到的一些问题和解决的办法,还有以及自己的理解。

资料中用的显示屏是CAT类型的,当然LED也兼容CAT的协议,其次就是分辨率的问题资料中是640 X 480,刷新频率是60HZ,(简单的说就是图像更新的时间是1/60s)像素时钟是25MHZ,我们的板子时钟是50MHZ所以要进行一个二分频,下面是我的模块,一个顶层模块,一个分频模块,一个vga显示的模块,我是直接把代码下载到FPGA中所以只有这三个模块,毫无疑问分频模块是为了将板子上50MHZ的时钟信号分频为25MHZ的时钟信号对于VGA显示的模块,我感觉可以划分为这么几个小的模块:计数(包括行和列)、有效区域(包括有效区域的定义和规定有效区域的坐标)、信号的产生、需要显示的内容。

由上面的6-2表可以看到行计数应该记到799,列计数应该记到520,行计数到799之后,也就是说第一行扫描完之后,垂直方向才开始计数。换的说法就是说行记到799,列方向加1。列方向直到记到520的时候才是一帧(也就是1/60S),每一行完成相应就会有一段时间的低电平,6-2表中已经给出,每一帧结束也会有低电平这段低电平的时间是两个行周期,也就是64us在6-2表也已经给出。

有效区域是指640X480的那段区域,开始扫描,最开始的一段时间是无效的这段无效的时间是Tpw和Tbp的和6-2的表中可以得到,然后就是定义一个新的坐标系,这个心的坐标系是针对有效区域来建的,接着就是同步信号的产生,接着就是你要在显示屏中显示的区域。

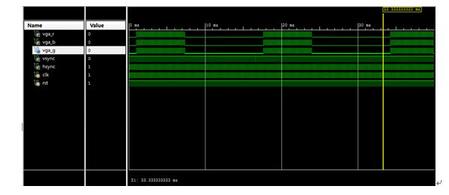

至于仿真,挺简单的,因为顶层模块中只有clk和rst两个信号,所以会很简单我用的ISE自带的仿真器Isim

放大之后

在这里分享一篇关VGA显示的文章名字叫《基于FPGA的VGA显示控制设计论文》写的挺好的!

用户452411 2013-10-28 13:22

用户437896 2013-10-23 19:43

1634090993_696409884 2013-10-23 15:56

用户437896 2013-10-21 15:27

用户403664 2013-10-21 09:58