本文为硬件原理图设计的通用规范,主要从基本的设计角度,总结一般公司的设计要求,整合而成。

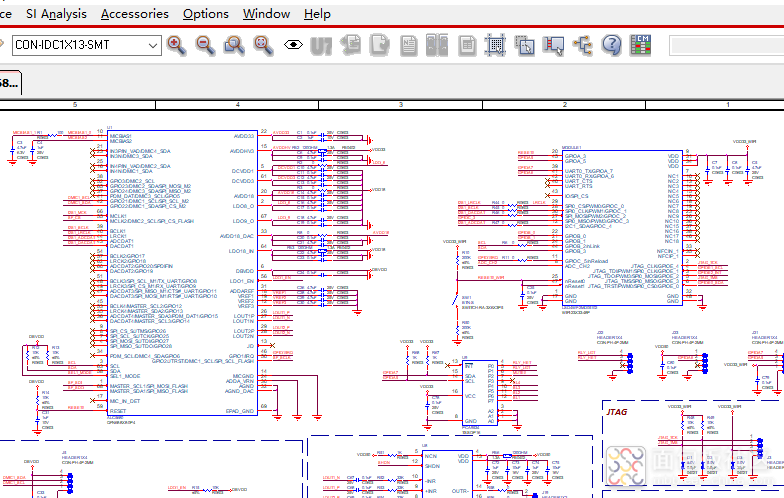

1. 原理图各页内容依次为:封面、目录、电源、时钟、CPU、存储器、逻辑、背板(母板)接口等。

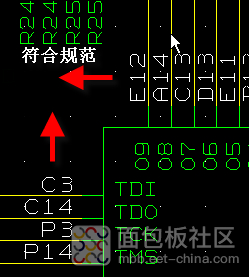

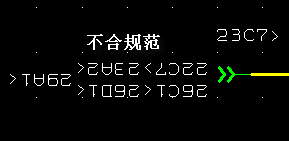

2. 原理图上所有的文字方向应该统一,文字的上方应该朝向原理图的上方(正放文字)或左方(侧放文字)。

下图分别为符合规范和不符合规范的例子。

文字都向上或者向左,符合规范 文字方向不一致,有文字向右,字符重叠,不合规范

标注文字方向向下,不合规范。

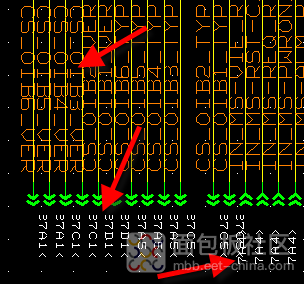

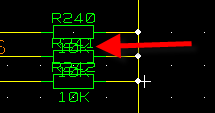

3. 原理图上的各种标注应清晰,不允许文字重叠。

原理图上包括网络名、位好、器件管脚号等各中字符都不允许重叠下面是不符合规范的例子

4. 元器件的位号要显示在该元件的附近位置,不应引起歧义。

5. 芯片的型号和管脚标注,精密电阻、大功率电阻、极性电容、高耐压电容、共模电感、变压器、晶振,保险丝等有特殊要求的器件参数要显示出来,LED应标示型号或颜色。

6. 有确定含义的低电平有效信号采用*或者_N(引入逻辑的需要用_N)后缀结尾。“有确定含义”包括但不限于如下信号:片选,读写,控制,使能。

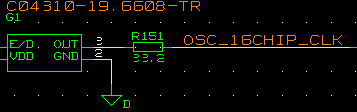

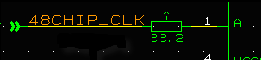

7. 所有的时钟网络要有网络标号,以CLK 字符结尾,以便于SI分析、PCB布线和检查;非时钟信号禁止以CLK等时钟信号命名后缀结尾。时钟信号命名应尽量体现出时钟频率信息。

为了方便信号完整性分析和布线约束制定,并保证不引起歧义,时钟信号必须以规定的CLK后缀结束。其他信号,例如时钟使能信号等,一律禁止以该信号命名后缀结束。时钟信号命名还应体现出时钟频率。根据绘图者的习惯,可以体现出时钟的流向、用途、来源等信息。

例如:FPGA1_8K_CLK,FPGA2_33M_CLK,OIB0_52CHIP_TCLK都是符合规范的命名。

串联端接时钟网络的命名参见串联端接网络的绘制和命名

8. 在PCB布线时有特殊要求的网络要定义网络名,推荐在原理图上注明要求。

9. 采用串联端接的信号(包括时钟),串阻在原理图上应就近放置于驱动器的输出端。串阻和驱动器之间不放置网络标号,串阻后的网络进行命名(时钟信号必须命名并满足时

钟信号的命名规范)。

对于源端端接网络,正确的画法应该是将串阻直接画在驱动器件的输出端,串阻和驱动器件之间的网络可以不进行命名,串阻之后的网络进行命名。如下图所示为一个正确的范例。

如果将串阻放在接收端,或者在串阻之前的信号进行命名,串阻之后的信号不进行命名,都会使得布线的分析和检查困难,甚至会造成串阻被放置在接收端而未被查出的结果,导致信号完整性较差。如下图是不正确的范例。

10 提供各单点网络列表和未连接管脚列表,并一一确认

关于单节点网络和浮空管脚的检查

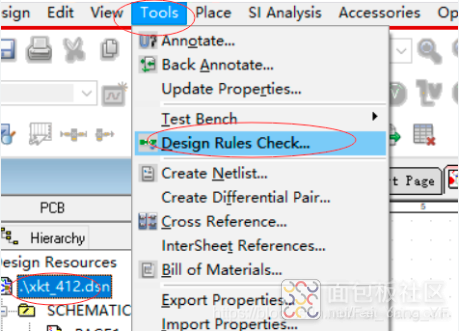

可以通过Cadence附带的原理图规则检查工具Rules Checker对原理图进行规则检查。我们最常用的是单节点(Single_node_net)和浮空管脚(Unconnected_instance)检查。

启动Rules Checker的方法是选择Allegro Project Manager的菜单Tools – Rules Checker。在Logic Rules一项中选择net_name_checks.rle中的single_node_net和Property_checks.rle中的unconnected_instance选项(根据需要可以继续选择nets_shorted等选项),运行Rules Checker。

运行完成的结果可以通过读取文本文件的方式检查,也可以通过View Marker直接在原理图上定位确认。

在设计中出现单节点和浮空管脚是很正常的事情,例如单板静电泄放模块中有很多单节点。本条目要求的是对所有的单节点和未连接管脚进行确认,确保没有漏接网络或者遗留未处理的CMOS输入管脚、器件控制管脚。

作者: 启芯硬件笔记, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-443713.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论