阻塞赋值和非阻塞赋值。

阻塞赋值:=

非阻塞赋值:<=

verilog有持续赋值(assign)和过程赋值(always、initial)。持续赋值针对网线类型,且只能使用阻塞的赋值方式。过程赋值针对寄存器类型,阻塞和非阻塞都可以用。

阻塞赋值。

module block(clk,a,b,c);

input clk;

input a;

output b,c;

wire a;

reg b,c;

always@(posedge clk)

begin

b = a;

c = b;

end

endmodule

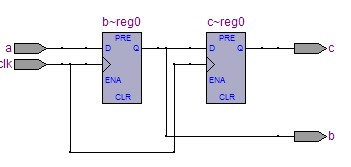

非阻塞赋值。

module non_block(clk,a,b,c);

input clk;

input a;

output b,c;

wire a;

reg b,c;

always@(posedge clk)

begin

b <= a;

c <= b;

end

endmodule

总结。

从名字上来区分。非阻塞赋值的的意思是赋值过程是不阻塞仿真流程的,赋值是在当前仿真时间结束前的最后一刻才进行的;阻塞赋值的意思是赋值过程是阻塞仿真流程的,只有赋值完以后,仿真才可以往下走。

考虑一下把非阻塞赋值程序改成下面这样,结果会怎么改变?

always@(posedge clk)

begin

b <= a;

#5

c <= b;

end

/1

/1

文章评论(0条评论)

登录后参与讨论