CRC码的FPGA实现之三仿真验证与时序分析

(3)建立波形仿真文件并进行仿真验证,分析其运行最高时钟频率。

使用Quartus II Simulator进行仿真设计

1.仿真设置

2.建立矢量波形文件

要对设计进行仿真,首先需要建立波形文件,也就是激励文件。选择File——New,在打开的对话框中选择 (矢量波形文件)。

(矢量波形文件)。

操作如下:

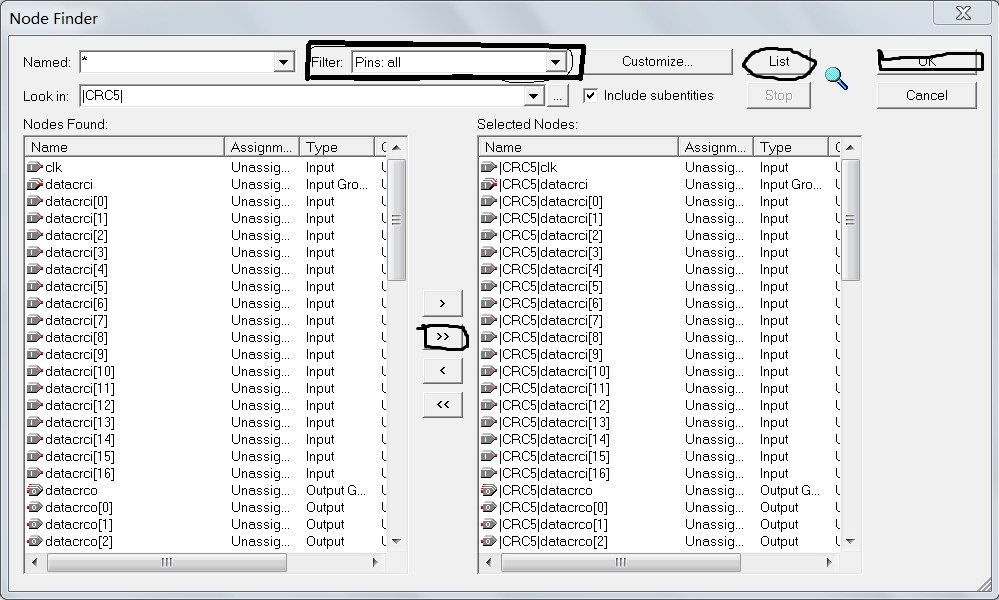

(1)将工程的端口信号选入波形编辑器中。选择Edit——Insert——Insert Node or Bus,出现Insert Node or Bus对话框,如下图

,将所有的信号加入至界面右边,结束后连续单击OK按钮。

,将所有的信号加入至界面右边,结束后连续单击OK按钮。

(2)设置仿真时间区域。

(3)波形文件存盘。

(4)编辑输入波形(输入激励信号)。

3.生成功能仿真网表文件

4.启动仿真器

5.观察仿真结果并查看仿真报告

6.分析输出信号波形

时序分析

时序分析方法有三种:第一种是通过全编译会自动运行时序分析;第二种是通过Processing——Start——Start Timing Analyzer命令;第三种是通过Tool——Timing Analyzer Tool命令,打开时序分析器工具。具体分析步骤如下:

分析该相关器所能运行的最高时钟频率(Fmax)及最大延时路径,并做记录。

/5

/5

文章评论(0条评论)

登录后参与讨论