CRC码的FPGA实现之二编译技巧

5.实验步骤

(1)启动Quartus II建立一个空白工程,然后命名为CCR5.v。

(2)新建Verilog HDL源程序文件,写出程序代码并保存,进行综合编译,完整的程序代码如下。

综合编译后会出现三个警告。

解决三个警告的方法如下:

第一个警告:

在设计中一定要将未定义的引脚定义为三态输入(使用的芯片冲突而损坏芯片。

解决方法如下

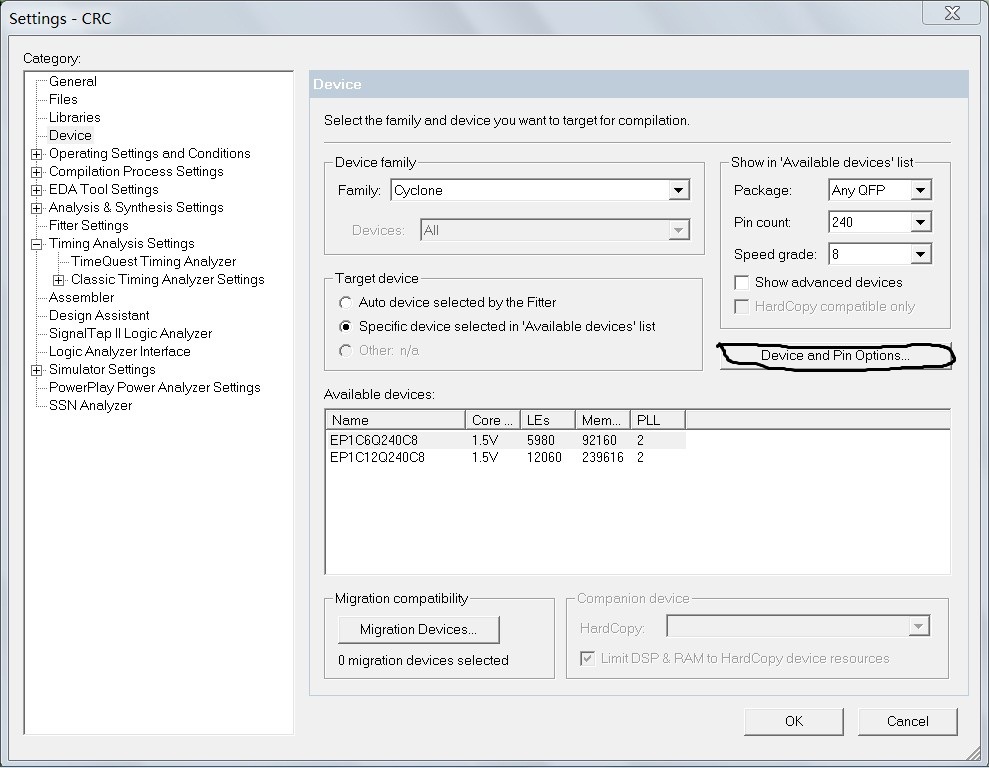

单击Assignments——Device,出现如下图

单击上图所示的Device&Pin Options,打开Device&Pin Options对话框。在该对话框中选择Configuration选项卡,并按下图进行设置即采用串行配置器件EPCS1的主动配置方式。

在对话框中选择Unused Pins选项卡进行没有使用引脚设置,按下图所示将未使用引脚设置为高阻输入,这样上电后FPGA的所有不使用引脚将进入高阻抗状态。

第二个警告:

第二个警告的意思是指发现clock节点没有定义成时钟信号。消除这个警告的方法如下:

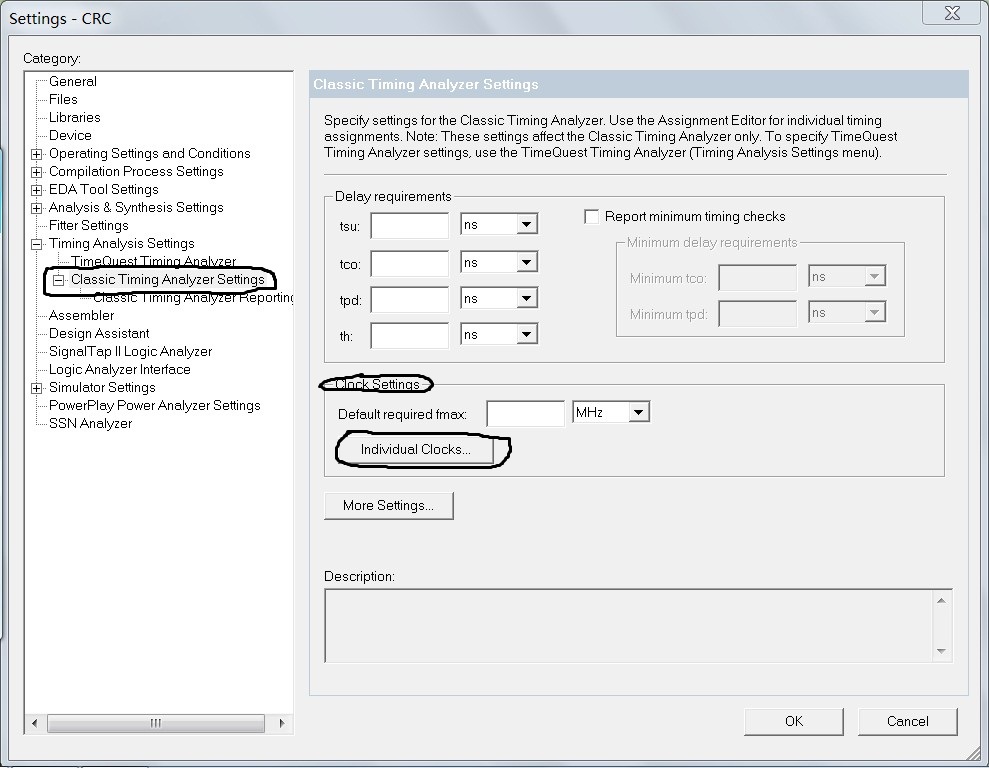

(1)选择Assignments——Device,选择 ,如下图所示,在对话框的Clock Settings选项区中单击Individual Clocks进行设置。

,如下图所示,在对话框的Clock Settings选项区中单击Individual Clocks进行设置。

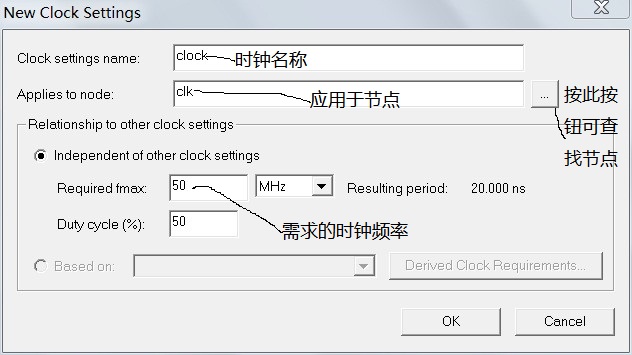

在弹出的对话框中单击New按钮添加节点,出现下图所示对话框,按图中所示进行设置。图中的Required fmax为系统需求的最大时钟频率。

设置好后连续单击OK按钮保存设置,最后进行编译,原先的这个Werning就会消除。以上的操作是将“clock”加入时钟域。如果“clock”不是一个时钟信号,可将设置属性改为“Not a clock”,也可以消除Warning。

第三个警告:

是指未分配引脚,引脚分配完后重新编译后这个警告便会消除。

/5

/5

文章评论(0条评论)

登录后参与讨论