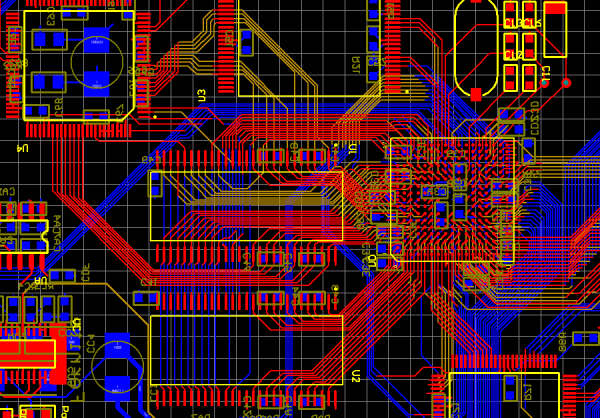

图中的蛇形线用途就是平衡各个NET的长度。从CPU出来到SDRAM的拓扑结构大约是CPU输出分支接2个SDRAM。这种分支结构在Protel里好像是没有办法自动做线长匹配的(应该是我比较笨,希望高手看到了予以指教),或者以后有空了学学专业的PCB软件,看看别的行不行。

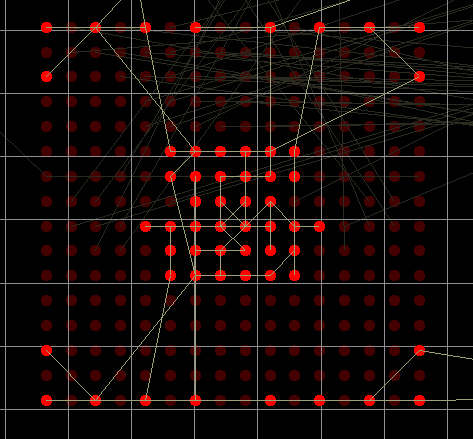

但是事实上,这块板子似乎没有必要做这么复杂的事情,我的大牛师兄的板子是这样的:

呵呵,他的拓扑结构是CPU->SDRAM1->SDRAM2,没有阻抗匹配。但是这样走线少,布线容易的多;再提供一个数据,他的最长和最短NET失配长度差达到37mm。但是人家的板子就是好使。我有个同学做了个CycloneII+SRAM的板,读写时钟也很高,啥匹配没有,就是好使。看来课本是不是应该改改了,哈哈。

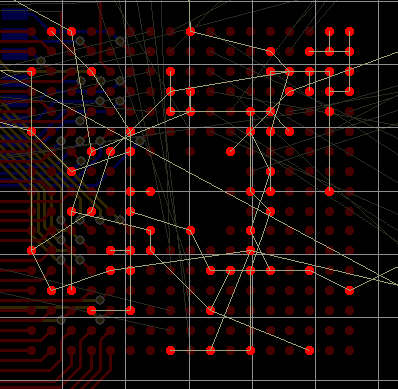

下面来抱怨下三星这个白痴公司,这是Analog Device的ADSPBF531的电源管脚分布

这是Altera的EP1C6F256的电源管脚分布

这是三星的S3C2410的电源管脚分布

希望我的原理图和封装都没有画错……真是无语了,一点也不为PCB工程师枉死的脑细胞考虑。看来韩国人毕竟是科技的暴发户,细节上完全比不上美国公司。不过回头来想想中国……我们连像样的单片机都生产不了,学IC设计的兄弟们,加油吧!

今天到这里。

/5

/5

文章评论(0条评论)

登录后参与讨论