时过一年多后,我又重新拾起了FPGA这个工具,重启FPGA学习之路。为什么我会突然又继续学习FPGA呢?因为我的学位论文里需要用到它,我想把那个项目做好,除此以外,我还觉得FPGA将是我今年(2016年)下半年找工作的主要方向,曾经我数次纠结是选择嵌入式(ARM)还是FPGA,经过仔细思考后,还是决定以FPGA为主、ARM嵌入式为辅,尽量做到精通FPGA、略懂ARM嵌入式。去年(2015年),英特尔斥巨资收购了FPGA的两大巨头之一的Altera公司,这个新闻在FPGA行业乃至整个电子信息行业都是很大的新闻。还记得上次听讲座时,东南大学的金石教授就透露英特尔收购Altera其主要目的是进攻无线通信领域,未来会推出内嵌ARM等微处理器硬核的FPGA器件,将被应用于5G通信系统中。说实话,这个新闻暗示了我们,FPGA会有更大的应用空间和市场,人才需求量也会剧增。所以说,我选择FPGA应该是没有错的。

前面说的都是些感概,现在正式进入主题。今天主要是复习Verilog的基本语法和Modelsim的功能仿真。

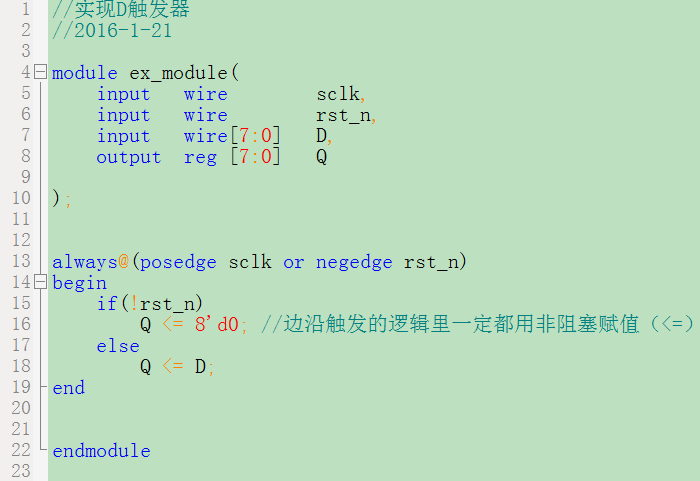

第一个例子是用Verilog描述一个D触发器,用异步复位的方式设计了一个有8位位宽的D触发器,由于此例简单,故在此不做多解释,直接贴出代码如下:

需要注意的问题:

(1)记住一条规则——时序逻辑用非阻塞赋值,组合逻辑用阻塞赋值。至于为什么?很难说清楚,现在只简单说一下,后期我会专门开一篇博文写阻塞赋值与非阻塞赋值。从功能上讲,非阻塞赋值更像时序逻辑电路,而阻塞赋值方式则更像组合逻辑电路。

(2)注意区分同步复位和异步复位。同步复位是指复位信号只有在时钟信号上升沿到来时才能产生复位动作,复位信号和时钟信号缺一不可,而异步复位则如例中所示那样,只有复位信号下降沿到来也能产生复位动作。两种复位方式哪种更好?很难说,看实际应用的需要吧,但一般情况下都使用异步复位的方式。

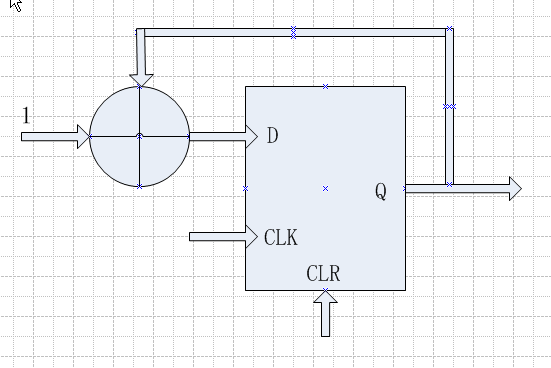

第二个例子是实现一个具有10位位宽的计数器,并用Modelsim仿真工具对设计的顶层模块进行功能仿真,验证加法器的功能是否正确。计数器的原理图如下所示:

图1 计数器的原理图

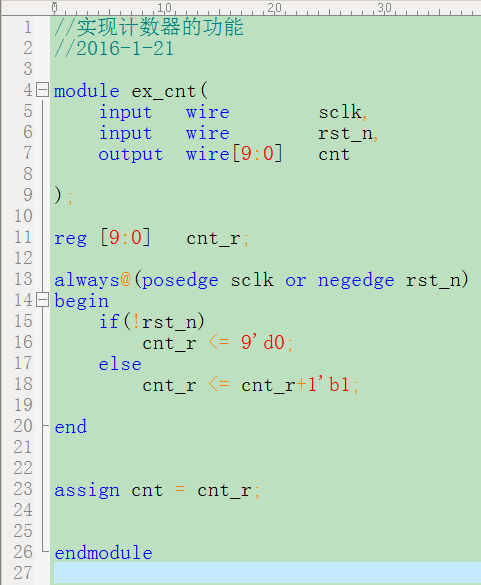

由图可知,计数器由加法器和D触发器两部分组成,加法器有两个输入,一个输入是常数1,另一个是引入触发器输出端的反馈信号,实现循环加1计数。D触发器的CLR端是复位信号,通常它就是Verilog代码中的rst_n信号。由于加法器的结构和原理都简单,故不多做解释,直接贴出代码的截图如下:

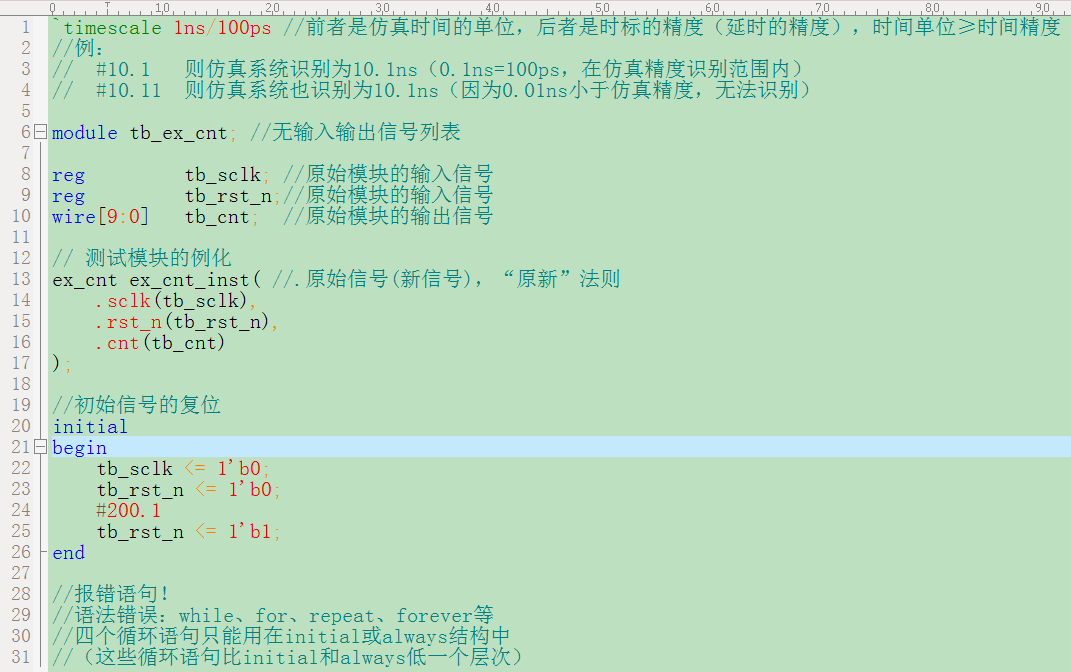

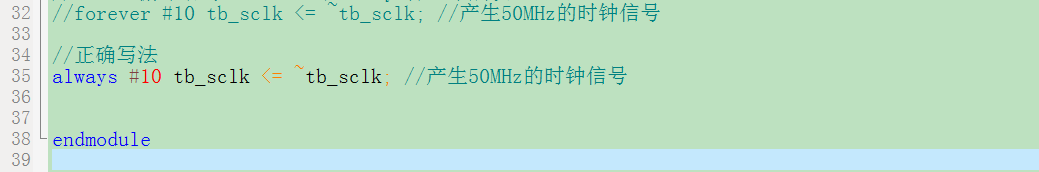

设计完模块电路后,就可以开始Modelsim功能仿真了。首先写Testbench文件,直接贴出代码如下:

写Testbench需要注意的问题已经写在代码注释中了,都是语法问题,不做过多介绍。仿真结果如下图所示:

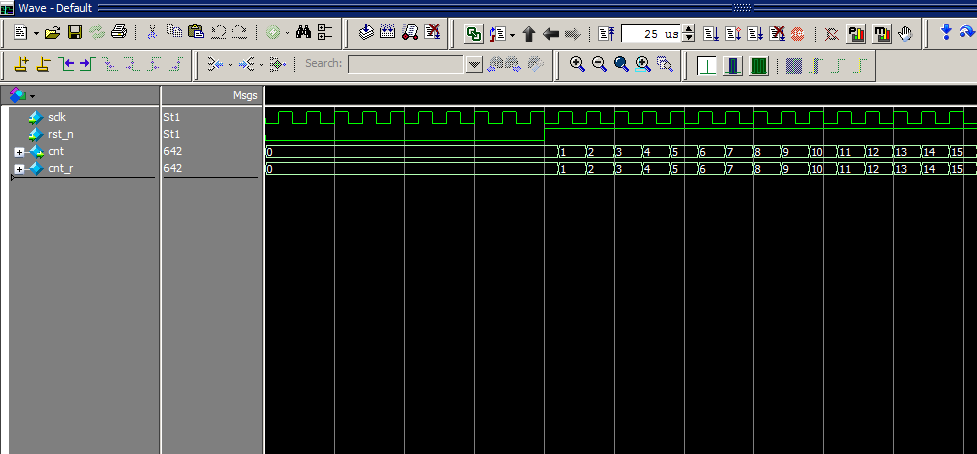

图2 仿真结果图1

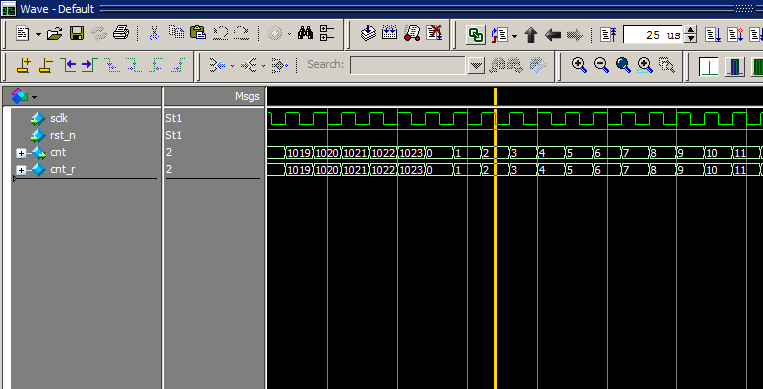

图3 仿真结果图2

由上图可知,仿真效果如Testbench所写的那样,在200.1ns时复位信号变为高电平(图2),结束复位动作,当下一个时钟上升沿到来时,计数器开始计数,当计数达到1023后(图3),再经过一个时钟周期计数值就会回到0,然后继续从0开始计数。

/2

/2

文章评论(0条评论)

登录后参与讨论