基于FPGA的GMSK调制<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

基于FPGA的GMSK调制<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

之高斯滤波器设计

先生成一个50kbps码率的源(带宽为25KHz),码元1编码成7FFFH(+1)发送,码元0编码成80000H(-1)发送。利用SystemView制作一个采样频率为500KHz的低通高斯滤波器,把生成的21阶滤波器系数做成.coe文件(如IIR filter的datasheet要求)加载到IP Core中生成所需低通滤波器。

最后将码元通过高斯滤波器进行滤波。

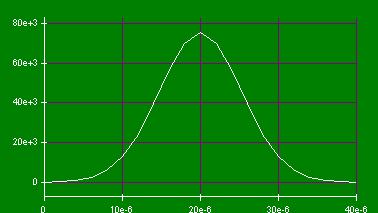

SystemView生成的高斯滤波器时域波形图:

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

SystemView生成的高斯滤波器频域波形图:

功能仿真波形如下。连续发送的码元为1011101001010101,最后通过高斯滤波后得到的平滑的波形如下,与原始码元型号一一对应。

布局布线后仿真的波形如下。可以看到有明显的毛刺。

Verilog程序:

module gmsktop(CLK,clk_50,RST,RDY,dout);

input CLK;//主时钟信号,500KHz

input clk_50;//50KHz时钟信号

input RST;

//input ND;

output RDY;

output[33:0] dout;

wire ND,RFD;

wire[15:0] source;

sent_source sent_source(clk_50,<?xml:namespace prefix = st1 ns = "urn:schemas-microsoft-com:office:smarttags" />RST,ND,RFD,source);

gsfir gsfir(ND,RDY,CLK,RST,RFD,source,dout);

endmodule

module sent_source(clk_50,RST,ND,RFD,source);

input clk_50;//50KHz时钟信号

input RST;//复位信号,高电平有效

input RFD;

output[15:0] source;//1bit基带信号,用16bit表示

output ND;

reg[15:0] source;

reg[15:0] scode;

reg[3:0] num;

reg ND;

always @(posedge clk_50)

begin

if(RST)

begin

ND <= 0;

source <= 16'd0;

num <= 4'b1111;

scode <= 16'b1011101001010101;

end

else if(RFD)

begin

if(scode[num]) begin source <= 16'h7fff; end

else begin source <= 16'h8000; end

ND <= 1;

num <= num-1;

end

else ND <= 0;

end

endmodule

用户1769355 2014-8-4 11:20

用户1769355 2014-6-22 17:39

正在弄这方面的东西

用户363685 2014-3-20 15:22

用户412764 2011-11-24 09:57

用户412764 2011-11-24 09:55

用户1565617 2011-10-9 23:09

用户1515086 2010-9-2 13:12

用户1403261 2010-5-27 14:34

用户1409644 2010-4-30 08:19

ilove314_323192455 2010-4-19 21:51