基于FPGA的SDRAM设计——模块化设计思路<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

题记:基于FPGA的SDRAM设计是个大题,以后多篇日志将会涉及到这个主题,今天先从总体上把握SDRAM的FPGA设计思想,也即介绍模块化的设计思路,以后还会具体深入的配合verilog源代码来展开介绍。(为了保持文章的原创性,本文的介绍文字均由特权同学根据自己的理解和认识用键盘实打实的敲上去的,其中难免有错误纰漏的地方,还望各位指点~_~ )

关于SDRAM基础知识的文章之前共享过了,那篇好文章,基本把SDRAM的相关知识点说得很到位了。从基本概念到SDRAM的时序操作都囊括了,在这篇日志的开始将会对这些基本知识再多做一些说明,以便下文更好的进入正题——模块化设计思路!

SDRAM是什么我就不多说了,它和平时我们接触比较多的SRAM不一样(计算机内存DDR SDRAM也是SDRAM,看看你家内存条上的八块芯片说的就是它了)。我们知道,FLASH和EEPROM断了电也能保存数据,SRAM只要不断电数据就会一直保存,而SDRAM光是上电并不能一直保存数据不丢失(那为什么计算机的内存用SDRAM而不用RAM或者ROM呢?答案就在于速度和成本吧!)。

SDRAM是基于电容储电的原理,这也是它就有别于SRAM的最主要原因,SDRAM在上电情况下最多能保存数据64ms,这是个上限吧,超过这个时间电容放电完成数据也就无法保存了,所以我们要做的就是先电容放电完成一步给电容提前充一次电,这个步骤就叫做prefresh(预刷新)。此外,我们知道在SDRAM的某一行数据被读写后,也会加大其功耗,促使其电容加快放电,所以我们在读写完某一行地址的数据后,就要做一步叫做precharge(预充电)的操作。

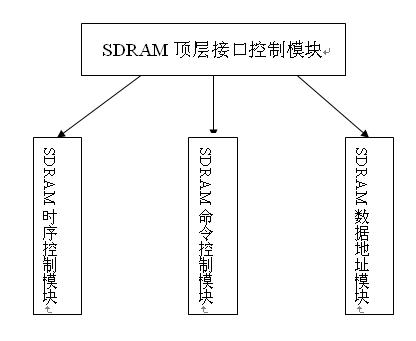

前面零散的说了点SDRAM相关的概念,下面系统的来给我们这个基于FPGA的SDRAM驱动设计分模块吧,然后我们再做具体深入不迟。

我是参考了很多有关SDRAM的verilog驱动,上面这个分模块方式是最常见的(最经典的)。顶层模块原则上是不做时序逻辑后者组合逻辑设计的,仅仅是定义接口,向上做成一个简单的封装,向下把三个模块粘合起来。时序控制模块里会把SDRAM从初始化到正常工作以及产生自刷新的请求和响应的时间关系做一个细化,其实说白了就是重点在这个模块里做各个状态的保持时间。命令控制模块会根据时序模块里产生的各个状态对FPGA和SDRAM的接口信号进行赋值,以达到相应的目的。数据地址模块就是要在指定的时间状态里读写SDRAM相应地址的数据。

用户1639510 2012-2-16 15:32

用户1639510 2012-2-16 15:04

用户340934 2011-8-4 11:18

ilove314_323192455 2011-8-3 13:40

用户340934 2011-8-3 12:24

ilove314_323192455 2011-1-24 08:28

用户183270 2011-1-23 19:51

ilove314_323192455 2010-12-31 16:08

用户249726 2010-12-31 15:44

用户1695575 2010-11-28 22:36