Quartus II Handbook, Volume 3 6-29<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

生成时钟(Generated Clocks)

Quartus II TimeQuest Timing Analyzer可以把修改或改变主时钟(或者引入时钟)特性的分频时钟、波纹时钟和电路作为生成时钟。

你可以定义这些电路的输出作为生成时钟。这些定义可以让Quartus II TimeQuest Timing Analyzer分析这些时钟以及关联的时钟网络延时(network latency)。

使用create_generated_clock命令定义生成时钟。

Example 6–5. create_generated_clock Command

create_generated_clock

[-name <clock name>]

-source <master pin>

[-edges <edge list>]

[-edge_shift <shift list>]

[-divide_by <factor>]

[-multiply_by <factor>]

[-duty_cycle <percent>]

[-add]

[-invert]

[-master_clock <clock>]

[-phase <phase>]

[-offset <offset>]

<targets>

Table 6–7. create_generated_clock Command Options

选项 | 描述 |

-name <clock name> | 生成时钟名 |

-source <master pin> | 指定被设定的时钟节点 |

-edges <edge list> | -edge_shift <shift list> | -edges指定和主时钟的上升沿和下降沿有关的新的上升沿和下降沿 |

-divide_by <factor> | -multiply_by <factor> | -divide_by和-multiply_by要素是基于第一个时钟上升沿,通过<factor>设定来延长或者缩短指定要素的波形 |

-duty_cycle <percent> | 指定生成时钟的占空比 |

-add | 允许你对同一个管脚添加多个时钟约束 |

-invert |

|

-master_clock <clock> | 用于主管脚上有多个时钟存在时指定一个主时钟 |

-phase <phase> | 指定生成时钟的相位 |

-offset <offset> | 指定生成时钟的偏移 |

<targets> | 指定被分配到的目标管脚 |

源延时是由于从主时钟(不一定是主管脚)开始的时钟网络延时所致。你可以使用set_clock_latency –source命令约束源延时。

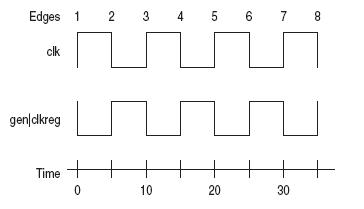

Figure 6–17 展示了如何产生一个基于10ns时钟的反向生成时钟:

Figure 6–17. Generating an Inverted Clock

create_clock -period 10 [get_ports clk]

create_generated_clock -divide_by 1 -invert -source [get_registers clk] \

[get_registers gen|clkreg]

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

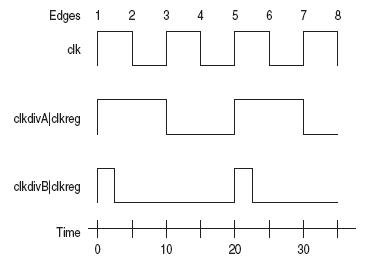

Figure 6–18 展示了如何使用-edges和-edge_shift选项以改变生成时钟。

Figure 6–18. Edges and Edge Shifting a Generated Clock

create_clock -period 10 -waveform { 0 5} [get_ports clk]

# Creates a divide-by-t clock

create_generated_clock -source [get_ports clk] -edges {1 3 5 } [get_registers \

clkdivA|clkreg]

# Creates a divide-by-2 clock independent of the master clocks’ duty cycle (now 50%)

create_generated_clock -source [get_ports clk] -edges {1 1 5} -edge_shift { 0 2.5 0 } \

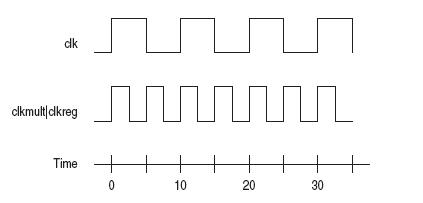

Figure 6–19 展示了-multiply_by选项对生成时钟的影响。

Figure 6–19. Multiplying a Generated Clock

create_clock -period 10 -waveform { 0 5 } [get_ports clk]

# Creates a multiply-by-2 clock

create_generated_clock -source [get_ports clk] -multiply_by 2 [get_registers \

/5

/5

文章评论(0条评论)

登录后参与讨论