<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

题记:时序分析摸索了很久,看了很多资料,也反反复复的对比总结,然后思考。现在总算有点大彻大悟的感觉了,但是还不够有些东西理解的可能还不是那么深入透彻,也喜欢把自己的思考过的东西拿出来和大家分享,更是希望大家能提出一些看法,在不断的讨论总结中才会有进步。

Quartus II TimeQuest Timing Analyzer综合设计约束支持设计管脚的约束。这些约束允许Quartus II TimeQuest Timing Analyzer执行系统静态时序分析,不仅包括FPGA的时序,而且包括了任何外部器件的时序以及板级时序参数。

输入输出延时 Input and Output Delay

使用输入输出延时约束来指定任何外部器件或者板级参数。当您应用这些约束,Quartus II TimeQuest Timing Analyzer将在整个系统执行静态时序分析。

设置输入延时 Set Input Delay

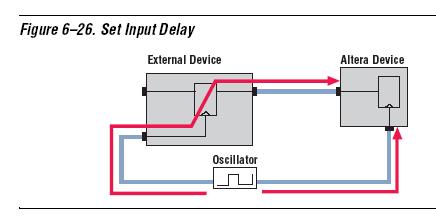

set_input_delay约束指定了某个管脚(器件I/O)关于给定时钟的数据到达时间。Figure 6–26 展示了一个输入延时的路径。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

使用set_input_delay命令来指定设计管脚的输入延时。Example 6–18展示了set_input_delay命令及选项。

Example 6–18. set_input_delay Command

set_input_delay

-clock <clock name>

[-clock_fall]

[-rise | -fall]

[-max | -min]

[-add_delay]

[-reference_pin <target>]

[-source_latency_included]

<delay value>

<targets>

Table 6–14. set_input_delay Command Options

选项 | 描述 |

-clock <clock name> | 指定时钟源 |

-clock_fall | 指定数据到达时间为时钟下降沿 |

-rise | -fall | 指定是时钟的上升沿或者下降沿延时 |

-max | -min | 指定是数据的最大或者最小到达时间 |

-add_delay | 另外增加一个延时,但是不会取代该管脚已经存在的延时 |

-reference_pin <target> | 从设计中指定的管脚或节点确定源和网络潜伏期。这有利于指定由某个时钟反馈的输出管脚相关的输入延时。 |

-source_latency_ included | 指定包括源潜伏延时值的输入延时值,因此任何分配给时钟的源时钟潜伏期将被忽略。 |

<delay value> | 指定延时值 |

<targets> | 指定目标管脚或者节点 |

如果您仅仅为输入延时值指定一个-max或者-min值,将会出现警告信息。此时未设定的输入最小延时值或输入最大延时值的缺省值和另一方相同。同样地,如果你仅仅为延时值指定一个-rise或者-fall值,也会出现警告信息。该默认延时值也会以和输入最大和最小延时值一样的方式设置。

最大值被用于建立时间检测,而最小值被用于保持时间检测。

默认情况下,输入延时(min/max, rise/fall)设置仅仅允许为一个clock, -clock_fall, -reference_pin组合。为一个相同的管脚指定输入延时值,若不想移除这些不同的clock, -clock_fall, 或者-reference_pin原先的输入延时设置,你必须指定-add_delay选项。当你指定了-add_delay选项,最坏的情况值将被采用。

-rise和-fall选项是相互排斥的,-min和-max选项也是相互排斥的。

设置输出延时 Set Output Delay

set_output_delay命令指定一个给定时钟相关管脚(器件管脚)的数据需要时间。使用set_output_delay命令指定设计管脚的输出延时约束。Figure 6–27展示了一个输出延时路径。

Example 6–19. set_output_delay Command

set_output_delay

-clock <clock name>

[-clock_fall]

[-rise | -fall]

[-max | -min]

[-add_delay]

[-reference_pin <target>]

<delay value>

<targets>

各命令选项和set_input_delay类似,这里略过。

其它说明和set_input_delay类似,这里也略过。

下面对I/O约束中关键的输入(输出)最大(最小)延时的概念做一些阐述。

从上图可以看到,输入最大/最小延时是针对外部器件的一些特性而进行设置的。所谓输入最大延时(这里先假设系统处于一个理想状态,即外部器件和FPGA共用一个时钟源,并且不考虑时钟偏斜,就是说时钟同步到达外部器件和FPGA的锁存沿),就是从时钟的发射沿算起,数据经过外部器件的最大Tco延时+PCB走线延时;而输入最小延时,就是数据经过外部器件的最小Tco延时+PCB走线的延时。这个时间和FPGA内部的建立保持时间又有怎样的关系呢?

和一般的时序分析一样,外部器件输入到FPGA的数据也必须满足建立保持时间要求,输入最大延时通俗的理解就是外部器件的数据到达FPGA端口的最晚时间,这个最晚时间可不能太晚,必须考虑FPGA内部锁存这个数据的建立时间Tsu。如果数据晚到时钟的锁存沿前的Tsu时间还没有到达,那么时钟就无法锁存这个数据了。那么就会出现时序违规了,所以,这个输入最大延时需要满足的第一个条件就是Tsu+输入最大延时<时钟周期TCLK(即上图的第一个公式)。

同理,这个数据要到达FPGA最快的时间称之为输入最小延时。这个最快时间也不能太快,试想想,如果在时钟的发射沿外部器件里的数据在非常短的时间内通过了外部器件的Tco和PCB走线,到达FPGA端口时,假设此时FPGA正出于上一个从外部器件传递来的数据的保持时间Th内,那么新到达的数据势必会破坏了前一个数据的保持时间,这也会造成时序违规。这么说来,这个输入最小延时也不能太小,也必须满足一定的条件,这个条件就是:Th<输入最小延时(即上图的第二个公式)。

讨论了这么多,相信你该理解了。那么我们再加上PCB时钟偏斜,时钟偏斜的概念我也不多说,你可以理解为这个参数是源时钟在PCB布线传输信号到达相应的锁存端口时间是会有一定偏差的,那么这个偏差就是PCB时钟偏斜,那么为什么是减去这个值而不是加上这个值呢?你可以理解这个PCB时钟偏斜值=时钟源到达FPGA端口时间-时钟源到达外部器件端口时间,然后~~慢慢消化吧!

建议大家参看Wind330博友的文章《同步时序约束之INPUT_DELAY详解》:

http://blog.ednchina.com/wind330/194897/message.aspx

输入最大/最小延时的概念说的很明白了,至于输出最大/最小延时的理解也很类似。上图的第一个公式其实和输入最大/最小延时的第一个公式有异曲同工之妙,只是把减数的位置互换了一下,不难理解。

但是第二个公式,我个人理解和altera官方的教程里提出来的不太一样,我的理解是这样的:FPGA输出数据达到外部器件输入管脚最快的时间=Tco+PCB布线延时,而根据输入最大/最小延时中第二个公式的分析,外部器件的Th应该小于上面的值,即外部器件的Th< Tco+PCB布线延时(先不讨论PCB时钟偏斜),那么Tco>Th-PCB布线延时才对,而不是Tco>输出最小延时=Th+PCB布线延时。

上面是我对这个公式的理解,也许分析得不对,期待高手指点!

用户598257 2014-7-1 10:26

用户428044 2013-1-23 15:58

用户1323656 2011-8-26 09:43

ilove314_323192455 2009-2-11 18:30

用户377539 2009-2-11 15:17

ash_riple_768180695 2009-2-11 07:27

ilove314_323192455 2009-2-10 22:38

ilove314_323192455 2009-2-10 22:35

ash_riple_768180695 2009-2-10 21:35

ilove314_323192455 2009-2-10 19:08