Quartus II Handbook, Volume 3 6-41<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

获得时钟不确定时间 Derive Clock Uncertainty

使用derive_clock_uncertainty命令应用于交互时钟(inter-clock)、内部时钟(intra-clock)和I/O接口的不确定时间的自动检测。建立和保持不确定时间都适合于时钟到时钟的传输。Example 6–16展示了derive_clock_uncertainty命令选项。

Example 6–16. derive_clock_uncertainty Command

derive_clock_uncertainty

[-overwrite]

[-dtw]

Quartus II TimeQuest Timing Analyzer自动的添加设计中时钟到时钟传输的时钟不确定时间。随着set_clock_uncertainty命令已被应用于源和目的时钟对中的任何时钟不确定时间约束,比起由derive_clock_uncertainty命令约束的时钟不确定时间具有更高的优先权。例如,如果set_clock_uncertainty命令先指定了源时钟CLKA和目的时钟CLKB之间的时钟网络延时。那么derive_clock_uncertainty命令次之,由derive_clock_uncertainty命令计算出的由源时钟CLKA到目的时钟CLKB的不确定时间将被忽略。

你可以使用-overwrite命令覆盖原先的时钟不确定时间分配,后者手动添加remove_clock_uncertainty命令进行移除。

在以下的时钟到时钟传输类型中,时钟必然能够出现,它们被derive_clock_uncertainty命令自动归类。

■ Inter-clock

■ Intra-clock

■ I/O Interface

交互时钟传输 Inter-Clock Transfers

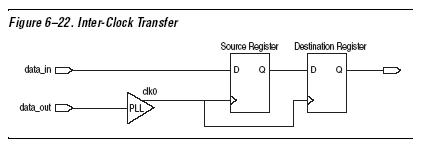

交互时钟传输(Inter-clock transfers)发生在FPGA核和来自内部PLL输出节点或管脚的源与目的时钟的寄存器到寄存器传输。Figure 6–22展示了一个交互时钟传输的例子。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

内部时钟传输 Intra-Clock Transfers

内部时钟传输(Intra-clock transfers)发生在FPGA核和来自内部PLL输出节点或管脚的源与目的时钟的寄存器到寄存器传输。Figure 6–22展示了一个内部时钟传输的例子。

I/O接口时钟传输 I/O Interface Clock Transfers

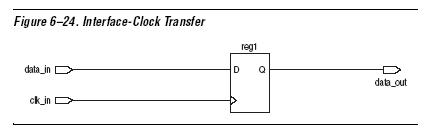

I/O接口时钟传输发生在数据从I/O端口到FPGA核(input)或者从FPGA核到I/O端口(output)时的时钟传输。Figure 6–24展示了一个I/O端口时钟传输的例子。

约束I/O总线不确定时间,你必须生成一个虚拟时钟来约束输入和输出管脚(使用以虚拟时钟作为参考的set_input_delay和set_output_delay命令)。当set_input_delay或者set_output_delay命令以PLL输出作为参考时钟管脚时,虚拟时钟需阻止derive_clock_uncertainty命令应用于交互或者内部时钟传输在I/O总线时钟传输的确定时钟。

产生的虚拟时钟应该和驱动I/O端口的源时钟具有相同的属性。例如,Figure 6–25展示了一个典型的具有时钟说明的输入I/O接口。

Example 6–17展示了用SDC命令来约束Figure 6–25中的I/O接口。

Example 6–17. SDC Commands to Constrain the I/O Interface

# Create the base clock for the clock port

create_clock –period 10 –name clk_in [get_ports clk_in]

# Create a virtual clock with the same properties of the base clock driving

# the source register

create_clock –period 10 –name virt_clk_in

# Create the input delay referencing the virtual clock and not the base

# clock

# DO NOT use set_input_delay –clock clk_in <delay_value>

# [get_ports data_in]

set_input_delay –clock virt_clk_in <delay value> [get_ports data_in]

用户422795 2012-2-9 19:32

ilove314_323192455 2011-10-31 10:38

用户379514 2011-10-28 20:00

用户1033024 2011-7-29 09:22

ilove314_323192455 2011-7-21 15:19

用户156476 2011-7-21 11:56

用户1570367 2011-7-20 22:56

用户1407990 2011-7-18 10:32

用户120337 2011-7-12 22:21

用户168062 2011-7-12 09:33