<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

记得之前遇到过一个很蹊跷的仿真问题,见《Altera调用Modelsim仿真奇怪的复位问题》。这次也遇上了一个很类似的问题,但是发现了根本原因之所在。

是这样的,一个测试中写一个下面的一段代码:

//--------------------------------------------------

// VGA色彩信号产生

reg[23:0] vga_rgb; // VGA色彩显示寄存器

always @ (posedge clk or negedge rst_n)

if(!rst_n) vga_rgb <= 24'd0;

else if(!valid) vga_rgb <= 24'd0;

else vga_rgb <= 24'hff_00_ff;

//r,g,b控制液晶屏颜色显示

assign lcd_r = vga_rgb[23:16];

assign lcd_g = vga_rgb[15:8];

assign lcd_b = vga_rgb[7:0];

很明显,这段代码里的vga_rgb寄存器的bit15-7是不变的,始终为低。而这样的代码在仿真时,vga_rgb的值却出现了一些意外:

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

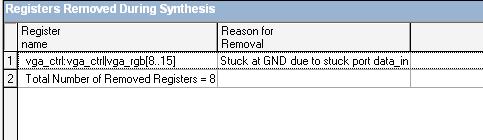

也就是vga_rgb的bit15-7虽然我们让他始终保持低电平,但是仿真结果却是高阻态。为什么呢?回头看看综合报告:

说明vga_rgb[8:15]被综合掉了,即所谓removed registers,所以这个8位寄存器不存在了, 仿真时也就只能以8’hzz代替了。将代码改成:

//--------------------------------------------------

// VGA色彩信号产生

reg[23:0] vga_rgb; // VGA色彩显示寄存器

always @ (posedge clk or negedge rst_n)

if(!rst_n) vga_rgb <= 24'd0;

else if(!valid) vga_rgb <= 24'd0;

else vga_rgb <= 24'hff_ff_ff;

//r,g,b控制液晶屏颜色显示

assign lcd_r = vga_rgb[23:16];

assign lcd_g = vga_rgb[15:8];

assign lcd_b = vga_rgb[7:0];

这样vga_rgb的所以24个寄存器都可能出现变化,所以也就不会被综合掉,那么仿真后是否正常呢?

得到预期的结果。即所谓寄存器不一定是寄存器,关键还是要看综合报告。

用户377235 2014-9-3 15:44

用户1721897 2013-11-20 21:12

用户1694070 2013-10-27 21:04

特权大哥,我并没有全看明白你的代码,但是我有个疑问,问什么要检测被乘数是否为1呢?检测乘数不是更简单吗?比如:两个4位数相乘yout=ain*bin。每次判断if(bin[i]),成立那么就把被乘数左移,然后yout=yout+ain<<i

用户1663879 2009-6-2 16:11

tengjingshu_112148725 2009-5-31 08:46