SDHC控制器代码移植日记二(SD_CMD_SERIAL_HOST)

<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

3. SD_CMD_SERIAL_HOST模块

3.1 接口连接框图

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

图3

3.2 接口定义与说明

//系统信号,时钟和复位

input SD_CLK_IN; //输入时钟信号

input RST_IN; //同步复位信号,高有效

//连接到SD_CMD_MASTER模块

input [15:0] SETTING_IN; //当前命令的设置定义

/*SETTING_IN位描述:

bit[15]--1,保留

bit[14:13]--word select

bit[12]--block read

bit[11]--block write

bit[10:8]--timing values

bit[7]--CRC check ON/OFF

bit[6:0]--response size;即响应数据位宽,0表示无需响应

*/

input GO_IDLE; //复位并返回IDLE状态,GO_IDLE信号用于复位该模块,并使其进入IDLE状态,退出当前传输。

input [39:0] CMD_IN; //待发送的命令

input REQ_IN; //外部模块工作请求

input ACK_IN; //外部模块工作完成响应

output reg [39:0] CMD_OUT; //命令答复

output ACK_OUT; //该模块内部工作完成应答

output reg REQ_OUT; //该模块内部数据传送请求

output reg [15:0] STATUS; //模块的状态标志

/*STATUS位描述

bit[15:7]--保留

bit[6]--data available,状态为DLY_WO或DLY_READ时该位置高

bit[5]--CRC valid

bit[4]--CMD state L/H

bit[3:0]--state:0001--WRITE_WR,0010--WRITE_WO,0011--DLY_WR,0100--DLY_WO,0101--READ_WR,0110--DLY_READ

*/

//SD卡物理层CMD接口

input cmd_dat_i; //SD卡CMD输入信号

output reg cmd_out_o; //SD卡CMD输出信号

output reg cmd_oe_o; //SD卡CMD方向使能控制信号,0--input,1--output

//连接到SD_DATA_SERIAL_HOST模块

output reg [1:0] st_dat_t; //启动数据传输:01--启动块读;10--启动块写;11--停止

/*

该模块由6个逻辑块组成:FSM_COMBO,REG_SYNC,ACK_SYNC,COMMAND_DECODER,FSM_OUT,FSM_SEQ。

FSM_COMBO--通过组合逻辑控制状态的迁移;

FSM_SEQ--控制状态迁移;包括状态的复位;

REQ_SYNC/ACK_SYNC--用于降低跨时钟域亚稳态的两级寄存器;

COMMAND_DECODER--读SETTING_IN向量并存储设置和命令道内部寄存器(在FSM_OUT中被使用);

FSM_OUT--状态机的输出逻辑。

*/

3.3 模块功能描述

该模块与外部的SD/MMC卡直接通信,用于读或写命令到SD/MMC卡中。外部接口由clk(在其他模块驱动输出)和双向信号CMD两个信号组成。其中CMD信号由该模块输出的cmd_out_o,cmd_dat_i和cmd_oe_o三个信号来驱动。

系统信号SD_CLK_IN和RST_IN为模块内部工作的时钟和复位信号(高电平有效)。GO_IDLE信号和RST_IN信号作用一样,在任意状态下将整个模块的工作状态复位到初始化。

跨时钟域的数据通信通过两组REQ和ACK信号的握手进行同步。在外部模块发出工作请求之前,需要先给控制信号总线SETTING_IN和命令值总线CMD_IN赋值,然后可以发起一次工作请求,将REQ_IN置高,若干个时钟周期后,该模块会拉低ACK_OUT表示响应。模块内部的状态机会发送CMD_IN的命令给SD卡,同时根据SETTING_IN的要求做一些完成其他的一些工作要求,如开启CRC7校验并输出校验结果、写入命令后读取若干个bit的响应数据等。只要ACK_OUT处于高电平状态,模块内部锁存的SETTING_IN和CMD_IN的状态就不会改变。ACK_OUT保持低电平直到CMD传输周期结束。 当该模块有数据要传送时(如更新STATUS或CMD_OUT中的数据有效时),该模块在做其他任何操作之前,会置位REQ_OUT并等待外部模块的ACK_IN输入拉高。CMD_OUT即读取到得应答数据,从高位开始有效。STATUS信号表示了当前该模块的工作状态,用于外部模块执行相应的处理和监视。st_dat_t信号连接到SD_DATA_SERIAL_HOST模块(做数据读写的专门模块),用于指示数据读写操作的执行。

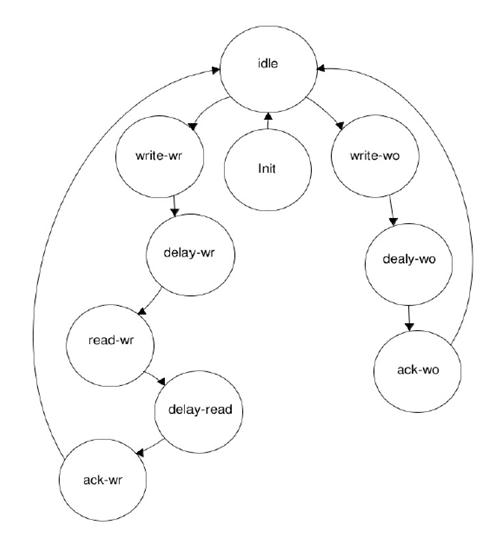

3.4 状态机工作图

图4

3.5 部分仿真说明

如图5所示,简单的产生ACK_IN/SETTING_IN/CMD_IN等激励,仿真波形输出的cmd_out_o(包括CRC7校验结果)以及其他一些寄存器输出都正常。

图5

/2

/2

文章评论(0条评论)

登录后参与讨论