有了前面两个实例的铺垫,下面这个工程就要带大家尝试搭建一个基于MicroBlaze的应用。特权同学也是第一次接插Xilinx的嵌入式开发平台,跑了一个流程下来,正如所料,和Altera的SOPC Builder(今后主推Qsys)以及EDS相比,单从开发环境上来看是大同小异、换汤不换药的。

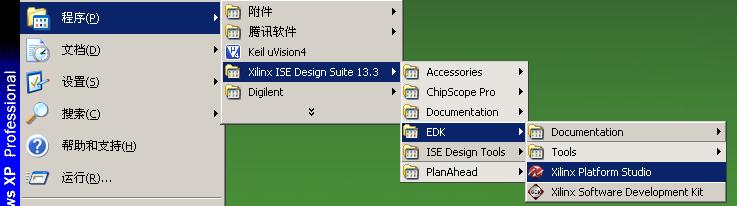

如图1所示,其实在安装ISE软件的时候,由于我们选择了Embedded Edition(可参考手记2),那么在安装完成的程序菜单中,如图1所示,EDK(Embedded Development Kit)后有两个开发平台,即Xilinx Platform Studio(硬件开发平台,简称XPS)和Xilinx Software Development Kit(软件开发平台,简称SDK),对应Altera的SOPC Builder(或Qsys)和EDS。由于Xilinx的SDK支持的软核MicroBlaze片内总线是AXI,而Altera的NIOS II主推的是Avalon,这里先不论孰优孰劣,他们之间多少还是有些区别的,非常习惯于SOPC Buider下工作的特权同学第一次接触XPS的环境还真有些不适应。而反观软件平台SDK,由于和EDS一样都是基于Eclipse的架构,所以比较容易上手,甚至连菜单按钮的布局和使用也多少有些似曾相识的感觉。

图1 EDK开发环境

相似归相似,咱们还是老老实实的找个傻瓜教程扎扎实实的熟悉一下整个开发流程。很自然的,特权同学便开启DocNav淘淘金,如图2所示,EDK and SDK下尽都是相关文档,而经过粗略的浏览后,特权同学锁定了“EDK Concepts, Tools, and Techniques.pdf”文档。虽然此文档也只是很简单的列举了一个软硬件协同开发的实例,很多设计细节都被忽略了(没让特权同学少吃苦头),但是好歹能够让人摸着大方向,于是花费不多时间特权同学便成功构建并验证了属于自己的第一个嵌入式工程(包括硬件工程和软件工程)。

图2 EDK和SDK相关文档

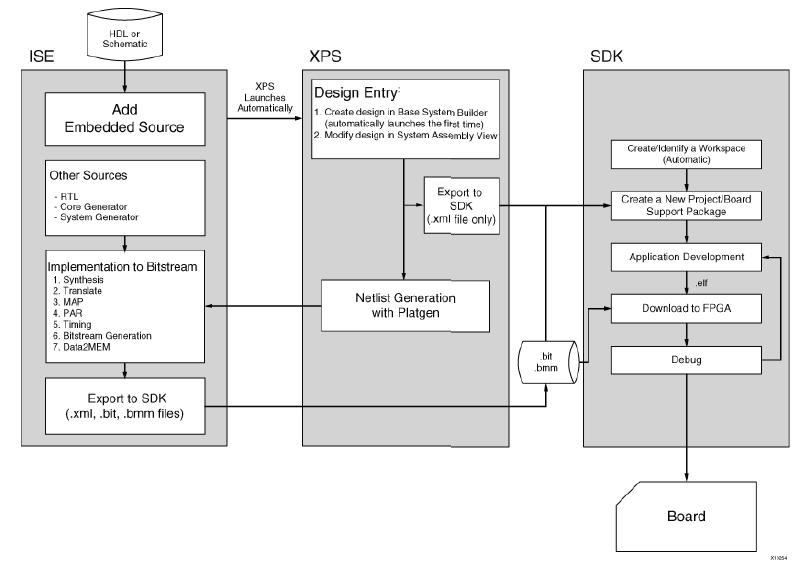

如图3所示,这里基本示意了整个软硬件开发的工作流程。从ISE基本设计输入开始,包括了XPS硬件系统架构的生成,再到SDK的软件开发,同时在ISE完成综合、约束、映射等编译步骤,最终生成可下载文件进行板级的调试验证。

图3 基本嵌入式工作流程

就着前面的开发步骤,我们也简单的跑跑流程好好体验一番。在上一个已经例化pll工程的基础上,我们接着使用XPS添加一个带MicroBlaze软核的嵌入式系统。

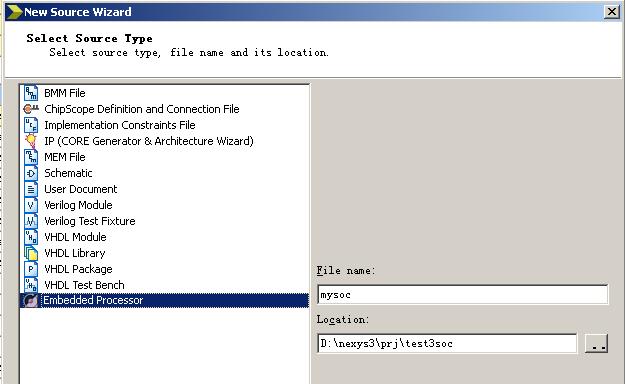

如图4所示,新建一个源文件,选择Embedded Processor,命名为mysoc。

图4 新建Embedded Processor文件

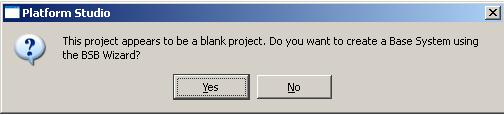

新建的Embedded Processor会自动打开XPS,然后首先弹出一个基本系统向导选择对话框,如图5所示。点击“Yes”。

图5 基本系统向导选择

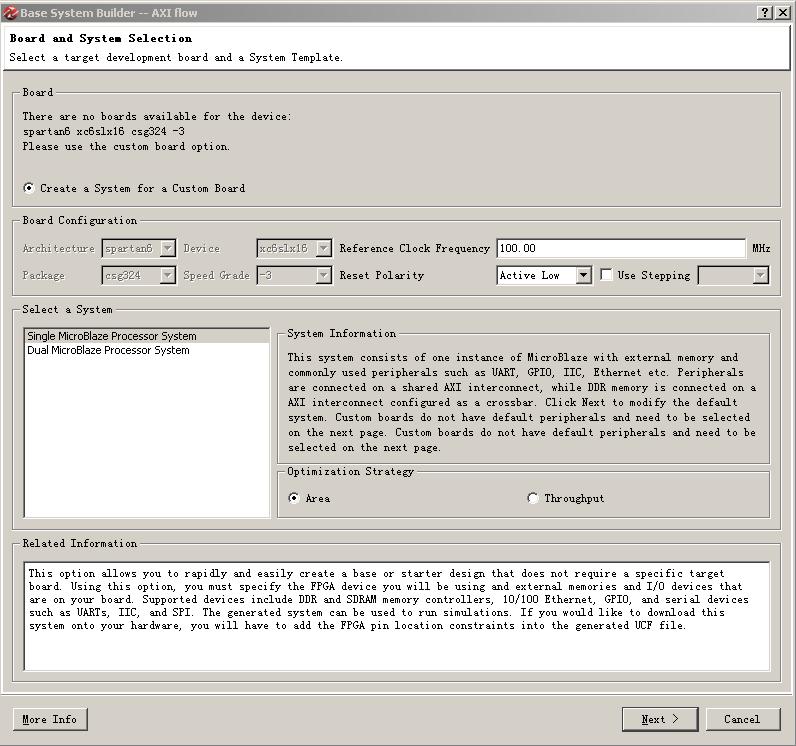

接着出现Base System Builder对话框,默认选择AXI system后点击“OK”。接着进入基本系统配置页面,这里主要由两个页面,第1个页面如图6所示。这里配置板级的信息和系统选择,板级信息如输入时钟频率,复位信号有效极性等,系统选择可以配置为单核或双核,优化策略可以是面积或吞吐量,该实例默认选择均符合要求,无需改动,点击“Next”到配置页面2。

图6 基本系统设置页面1

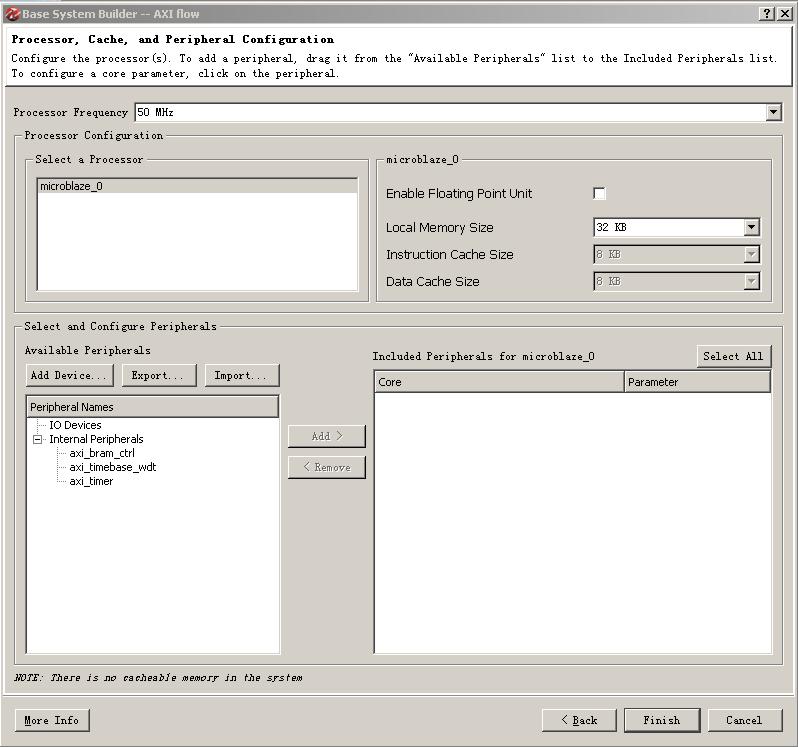

如图7所示,在配置页面2中,选择Processor Frequency为50MHz,设置Local Memory Size为32KB。接下来需要添加一个8bit的GPIO外设,点击“Available Peripherals”下的“Add Device…”按钮。

图7基本系统设置页面2

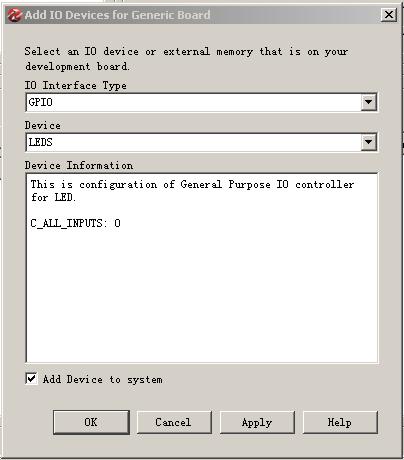

弹出“Add IO Devices for Generic Board”窗口如图8所示,分别设置“IO Interface Type”为“GPIO”、“Device”为“LEDS”,完成后点击“OK”。

图8 添加GPIO外设

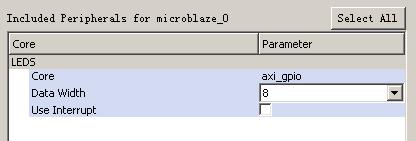

此时,在“Included Peripherals for microblaze_0”下出现如图9所示的LEDS外设,默认设置Data Width为8。最后我们点击Finish完成向导配置。

图9 新添加的LEDS外设

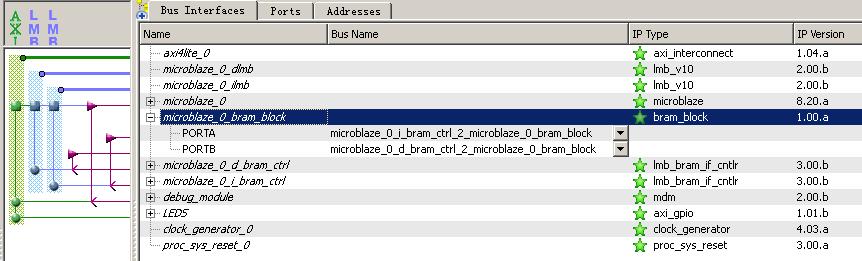

稍等片刻,当新系统生成好之后,如图10所示,在XPS默认打开的System Assembly View的Bus Interfaces列表中,这个新系统的所有组件都罗列出来了,并且在左侧有各个组件间的信号接口连接关系。从他们之间的相互连接关系很容易便可理解这个简单系统的架构方式:microblaze_0便是大名鼎鼎的软核CPU——MicroBlaze,它连接了AXI总线用于外设扩展,这条总线上挂着的外设包括了我们特意添加的GPIO外设LEDS;此外,microblaze_0的两个LMR接口分别连着microblaze_0_i_bram_ctrl和microblaze_0_d_bram_ctrl,从命名上不能推断出着两个组件应该是CPU的指令(instruction)和数据(data)存储控制器,而靠右侧的红色连接部分又分别将他们与microblaze_0_bram_ctrl组件相连接,说明这个microblaze_0_bram_ctrl便是CPU的主存储控制器。此外,两个相对独立的clock_generator_0和proc_sys_reset_0则为系统时钟和复位产生组件。

图10 IP组件列表

/5

/5

文章评论(0条评论)

登录后参与讨论