接着我们来看看Ports部分,如图11所示。这里展开External Ports便是该系统所有需要与外部进行直接隐射的管脚。LEDS_TRI_O便是8个连接到板上指示灯的信号,RESET是低电平有效的复位信号,而CLK_N和CLK_P是一对100MHz输入的差分信号。由于我们的外部输入100MHz时钟不是差分的,而是单时钟接口,因此需要简单的做些修改。

展开clock_generator_0,在CLKIN一栏右击选择“New Connection”,此时如图12所示,差分时钟便成了单时钟接口了。鼠标落在这个单时钟信号上再次右击并选择“Make External”,这个单端时钟接口便出现在了External Ports中。而之前的差分时钟接口并未在External Ports中消失,需要依次右击并选择“Delete External Ports”便可将其删除。

图11 系统外部连接信号

图12 更改后的CLKIN

修改好之后的External Ports列表如图13所示。

图13 更改后的External Ports

完成时钟信号修改,点击XPS菜单栏HardwareàGenerate Netlist生产这个嵌入式硬件系统的网表。回到ISE中,在Hierarchy下多出了mysoc.xmp文件,选中它。在Processes下展开Design Utilities,双击View HDL Instantiation Template生产系统的例化模板文件,如图14右侧所示。

图14 生成系统例化模板

将此模板复制到ISE顶层源代码中,相应匹配好接口,原先的8个LED接口将由软件编程控制。顶层源代码修改如下:

module testled(

clk,rst_n,

led

);

input clk; //100MHz

input rst_n; //低电平复位信号

output[7:0] led; //连接到LED指示灯

wire clk_100m; //clocking输出100MHz

wire clk_50m; //clocking输出50MHz

wire clk_25m; //clocking输出25MHz

wire clk_12m5; //clocking输出12.5MHz

wire clk_locked; //clocking输出完成标志位

//---------------------------------------------------

//IP核Clocking Wizard例化

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

myclocking uut_myclocking

(// Clock in ports

.CLK_IN1(clk), // IN

// Clock out ports

.CLK_OUT1(clk_100m), // OUT

.CLK_OUT2(clk_50m), // OUT

.CLK_OUT3(clk_25m), // OUT

.CLK_OUT4(clk_12m5), // OUT

// Status and control signals

.RESET(!rst_n),// IN

.LOCKED(clk_locked)); // OUT

// INST_TAG_END ------ End INSTANTIATION Template ---------

//---------------------------------------------------

// 例化mysoc系统

(* BOX_TYPE = "user_black_box" *)

mysoc uut_mysoc (

.RESET(rst_n),

.LEDS_TRI_O(led),

.clock_generator_0_CLKIN_pin(clk_100m)

);

endmodule

最后我们双击“Generate Programming File”完成硬件系统的编译和下载文件生成。

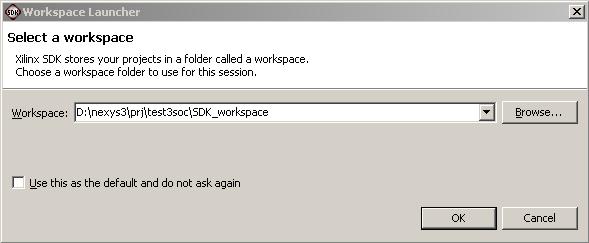

下一步我们把平台转移到SDK,在工程目录下新建一个名为SDK_workspace的文件夹,然后打开SDK时需要选择一个workspace,如图15所示,对应定位到SDK_workspace文件夹下即可。

图15 workspace设置

进入SDK后,菜单栏上选择FileàNewàXilinx C Project,然后在“New Hardware Project”中输入Project name,并选择工程目录下的mysoc\__xps\system.xml作为Target Hardware Specification。此配置页面主要是设置软件工程的硬件平台。

图16 硬件平台配置页面

下一配置页面如图17所示,这里设置软件工程的Project name,并且选择Select Project Template为“Empty Application”。其余选项使用默认,完成设置。

图17 软件工程配置页面

此时在Project Explorer下出现了mysoc_hw_platform、empty_application_bsp_0和example_application_0三个文件夹。在example_application_0上右击并选择NewàSource file,新建一个名为main.c的源文件,如图18所示。

图18 软件工程文件夹

在main.c中编写一段简单的流水灯测试代码,如下所示:

/* ------------------------------------------------------------ */

/* Include File Definitions */

/* ------------------------------------------------------------ */

//#include "xil_types.h" //This file contains basic types for Xilinx software IP.

#include "xparameters.h" //The hardware configuration describing constants

#include "xgpio_l.h" //This header file contains identifiers and driver functions

#define uchar unsigned char

#define uint unsigned short

/* ------------------------------------------------------------ */

/* delay function */

/* ------------------------------------------------------------ */

void delay(uint cnt)

{

uint i,j;

for(i=0;i;i++)<>

for(j=0;j<256;j++);

}

/* ------------------------------------------------------------ */

/* main function */

/* ------------------------------------------------------------ */

int main()

{

uchar m;

while(1)

{

for(m=0;m<8;m++)

{

XGpio_WriteReg(XPAR_LEDS_BASEADDR,1,(1<));<>

delay(10000);

}

}

return 0;

}

接着右键单击example_application_0并选择Builder Project对该软件工程进行编译。接着配置产生可在线烧录的.bit文件,这个.bit文件将包括硬件工程生成的.bit文件和软件工程烧录文件.elf。在XPS的菜单栏选择Xilinx ToolsàProgram FPGA,Program FPGA的配置如图19所示,Bitstream中选择硬件生成的配置文件testled.bit,一般就在工程目录下;BMM File中选择硬件系统文件edkBmmFile_bd.bmm,也在工程目录 下;最后在Software Configuration下点击ELF File to Initialize in Block RAM的下拉条找到example_application_0.elf即软件工程的烧录文件。

图19 FPGA烧录

原本Program FPGA用于在线烧录FPGA器件,但是Nexys3目前的USB连接方式并不直接支持(这个后面再研究,话说“白猫黑猫抓到老鼠都是好猫”,咱只要能下载进去就行),但是不要紧,我们还有Adept呢。这里配置一下待烧录文件的一些基本信息,然后点击Program后虽然会报错并提示无法成功烧录,但是与此同时在mysoc_hw_platform文件夹下生成了一个包含软硬件烧录的download.bit文件,最后我们使用Adept将这个文件下载到Nexys3中即可实现在线运行的流水灯了。

/5

/5

用户1741954 2014-3-28 21:16

用户1609127 2010-5-26 18:48