Qsys与uC/OS学习笔记1:与Qsys的第一次亲密接触

从Quartus II 11.0开始,喜新厌旧的Altera就不厌其烦的炒作SOPC Builder的替代者Qsys。记得去年参加他们的研讨会时就已经搬上台面, 版本12以后更是完全摒弃了SOPC Buider,如今12.0sp2都已经release了,如果再不加紧找个理由上Qsys练练手,咱可就要OUT了。

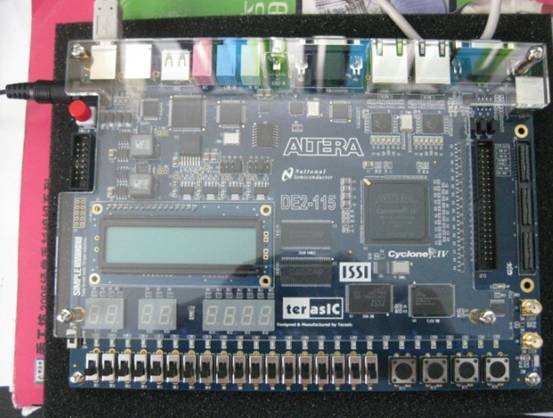

正好近期对uC/OS非常感兴趣,苦于手上没有一款比较高端的板子用于实践。于是通过层层关系最终在Altera的大学计划经理John处讨得一套TerasIC的DE2-115,板载EP4CE115F29C7N器件,丰富的片上资源和外设足以应付各种功能需求。上个图,让各位看官也垂涎三尺。

图1

废话就此打住,后面要上点有营养的文字。话说特权同学也是第一次接触Qsys,虽然这两天抽空恶补了一下Qsys的各种pdf,但毕竟学海无涯苦作舟,咱也就多懂了点皮毛,提前班门弄斧一下,只是实实在在的把自己知道的、明白的、领会的一一道来,其间肯定有疏漏和不妥之处,甚至也会带些疑问而来,还请高手不吝惜键盘跟帖指点。

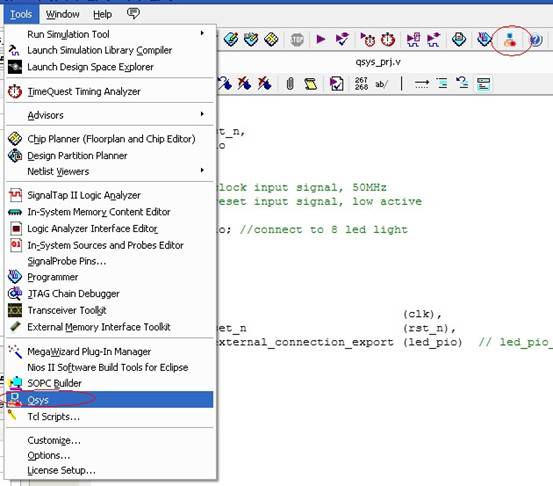

第一步当然是新建工程,这等小儿科步骤不详究,直接步入主题。如图2所示,两种方式均可打开Qsys。

图2

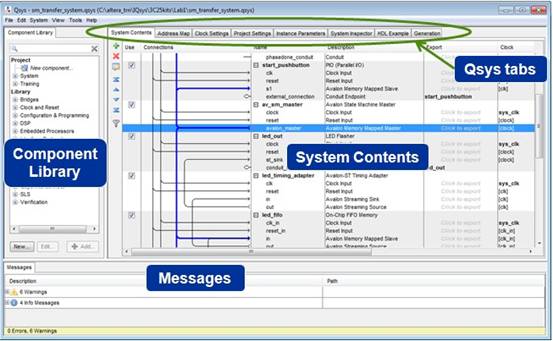

进入Qsys后,如图3所示,界面窗口的布局内容多少还有些似曾相识,毕竟还是SOPC Builder一脉相承的,一个最大的变化是Qsys tabs的选项要比SOPC Buider多得多,Qsys的更多系统个性化编辑和设置也都得益于此了。

图3

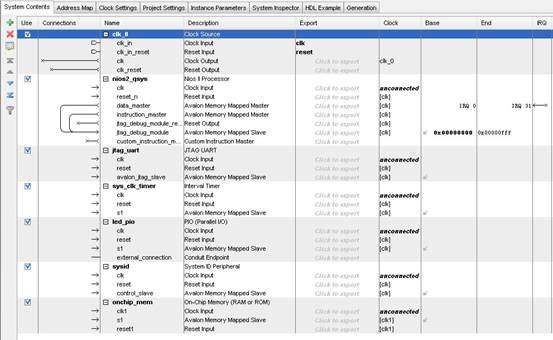

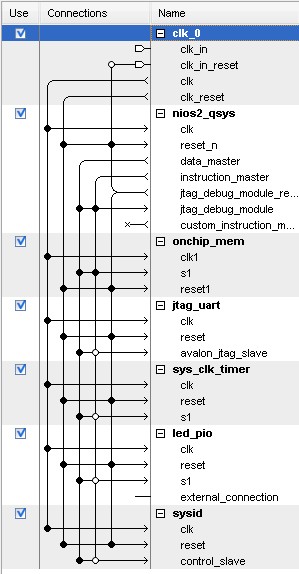

初次打开Qsys,System Content中默认已经添加了一个孤零零的CLOCK组件,其他啥也没有,光杆司令只是个摆设,啥活干不了。于是乎,咱在Component Library中各种查找,添加了几个常用组件,如NIOS II处理器、JTAG UART、定时器TIMER、8bit输出PIO、system ID和200KB的片内RAM。如图4所示,这些常用的组件各就各位,基本就可以搭建起一个最小嵌入式系统了,至少是可以写代码在线运行程序的。

图4

不过,图4咱可就有点看不懂了,SOPC Builder可不是这样,Connections应该是完全在添加组件过程中自动互联上才对的,而Qsys则一片空白,貌似啥都不连接,别说,还真这么回事。那么就这么着把,绝对不可以,人家系统肯定**。怎么办?自己动手,丰衣足食!找了相关资料,都说Qsys可以很智能的进行组件的互联,愣是没找到一个“智能按键”让他们自动互联,看来Altera把这项考验真水平的活都下放给最智能的人脑来干了,能不智能吗?哈哈,好了,还好特权同学底子不差,虽然以前都让SOPC Buider自动连接从不人工干预,但是实际接口都是牢记于心的,三下五除二便连接成功。如图5所示,看到小圆圈并点击后空心、实心就会变化,实心代表连接上了。这连接的活可好玩了,一点不比那些年不知道祸害了多少有志青年的“连连看”差多少,那比得是速度,咱比的是准确;那玩玩消磨时间,咱点点还能长知识呢。系统的连接其实也非常简单,我们的时钟clk和复位reset都没有做太复杂,都是clk_0组件输出,所以所有的组件都和clk_0的时钟复位连接上就对了;CPU的数据存储器和代码存储器都必须由片内RAM来担当,所以nios2_qsys的data_master和instruction_master均与代表onchip_mem的从机总线s1连接上。而其他作为总线slave的外设均连接到nios2_qsys的data_master上即可。

图5

另外,要说明的是作为系统与外部连接的接口不像SOPC Buider一样直接引出了,需要设计者特别设置一下。如图6所示,选择Export列的属性为*_external connection,然后该接口前面会出现一个export的图标。

图6

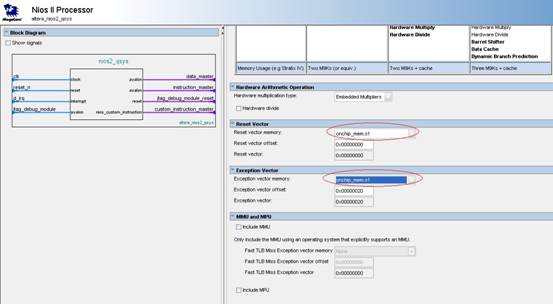

接着我们还要双击打开nios2_qsys组件,将其Reset Vector和Exception Vector均设为onchip_mem。如图7所示。

图7

就此,一个漂亮的测试系统搭建完毕,后面的事情就是分配地址、中断优先级等,这个可以如同SOPC Builder一样使用菜单栏上的自动分别选项一键分配。特权同学就常常这么干,咱对地址还真没讲究,中断优先级有时还可以根据需要调整一下。

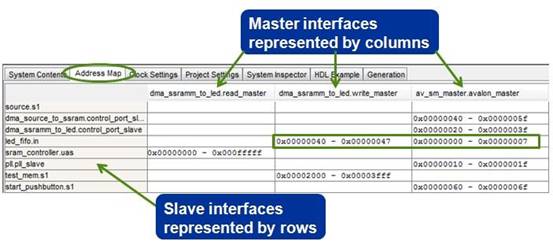

前面提到了Qsys tabs是一大特色,这里不一一细说,偷懒贴几张图。大家自己使用的时候可以慢慢体味。如图8,Address Map对地址的管理一目了然,而且对于不同的Master可以有不同的地址空间映射。

图8

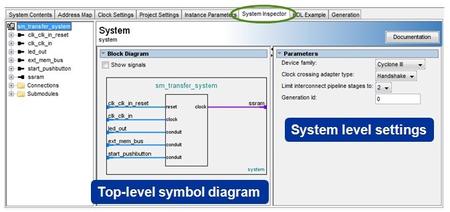

如图9所示,System Inspector中罗列所有的信号接口以及相关属性参数,甚至可以在此处进行修改。

图9

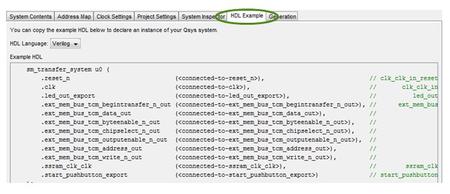

如图10所示,HDL Example中直接给出了当前系统的例化模板,直接复制到工程顶层模块后进行修改即可,这比之前专门要到工程目录下找相关文件查看要方便得多。

图10

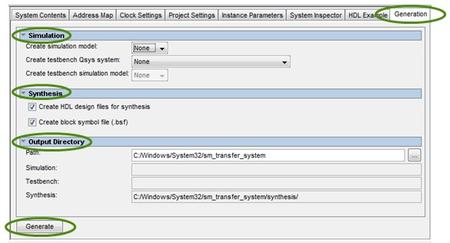

最后,如图11所示,Generation里可以选择系统仿真、综合以及各种输出的相关设置,最后点击右下角的Generate即可启动当前系统的生成。大家可别忘了在Output Directory中设置后系统输出路径。

图11

特权同学在该系统下跑了个软件模板工程Binary Counter,一切正常。

用户403664 2012-10-11 11:17

用户1696769 2012-10-11 11:15

用户424277 2012-10-10 16:27

用户1000403 2012-10-9 17:40

用户1417837 2012-10-7 20:51

ilove314_323192455 2012-8-25 13:19

用户421471 2012-8-24 09:19

Hoki 2012-8-24 08:37