CMOS Sensor接口时序约束

我们再看看PCB的走线情况,算算余下和PCB走线有关的延时。

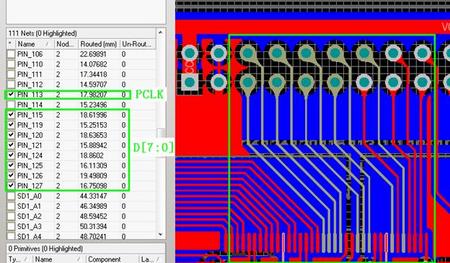

如图所示,这是PCLK和D[7:0]在SF-CY3核心板上的走线。

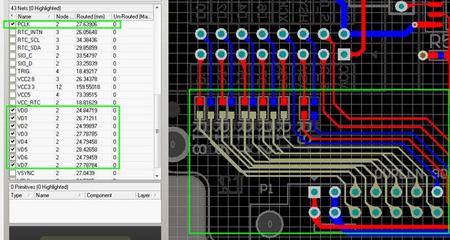

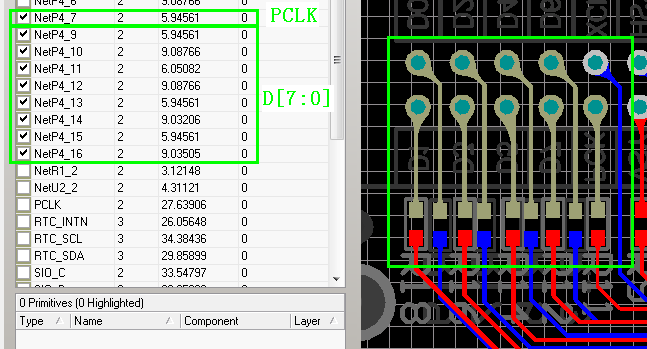

如图所示,这是PCLK和D[7:0]在SF-SENSOR子板上的走线,在这个板子上的走线由匹配电阻分两个部分。

根据前面的走线长度,我们可以换算一下相应的走线延时,如下表所示。因此,我们可以得到,Tcpcb_max = 0.35ns,Tcpcb_min = 0.35ns,Tdpcb_max = 0.36ns,Tdpcb_min = 0.31ns。

|

信号名 |

SF-CY3走线长度 |

SF-SENSOR走线长度1 |

SF-SENSOR走线长度2 |

总长度(mm) |

延时(ns) |

|

PCLK |

18 |

27.7 |

6 |

51.7 |

0.346023622 |

|

VD0 |

16.8 |

24.9 |

9.1 |

50.8 |

0.34 |

|

VD1 |

19.5 |

26.8 |

6 |

52.3 |

0.35003937 |

|

VD2 |

16.2 |

25 |

9.1 |

50.3 |

0.336653543 |

|

VD3 |

18.9 |

27.8 |

6 |

52.7 |

0.352716535 |

|

VD4 |

15.9 |

24.8 |

9.1 |

49.8 |

0.333307087 |

|

VD5 |

18.7 |

28.5 |

6 |

53.2 |

0.356062992 |

|

VD6 |

15.3 |

24.8 |

9.1 |

49.2 |

0.329291339 |

|

VD7 |

18.7 |

27.8 |

6 |

52.5 |

0.351377953 |

|

HREF |

14.6 |

23.8 |

9.1 |

47.5 |

0.317913386 |

将上面得到的具体数值都代入公式,得到:

Input max delay = (0 – 0.35ns) + 65ns + 0.36ns = 65.01ns

Input min delay = (0 – 0.35ns) + 8ns + 0.31ns = 7.96ns

加上一些余量,我们可以去input max delay = 66ns,input min delay = 7ns。

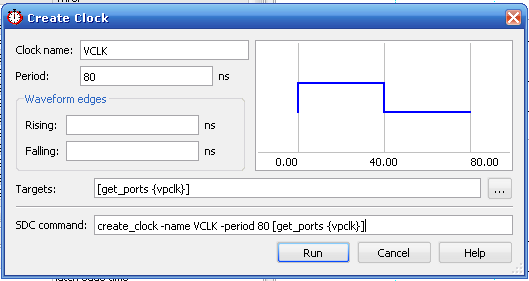

下面我们来添加时序约束,打开TimeQuest,点击菜单栏的ContraintsàCreat Clock,做如下设置。

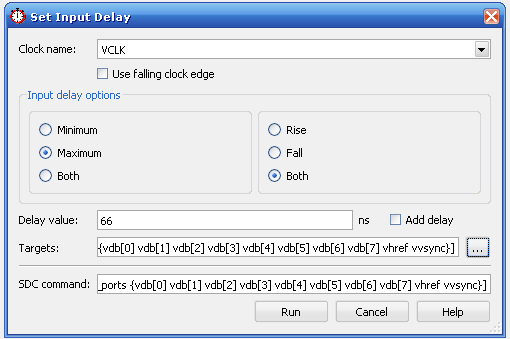

点击ContraintsàSet Maximum Delay,对vdb[0] vdb[1] vdb[2] vdb[3] vdb[4] vdb[5] vdb[6] vdb[7] vhref的set_max_delay做如下设置。

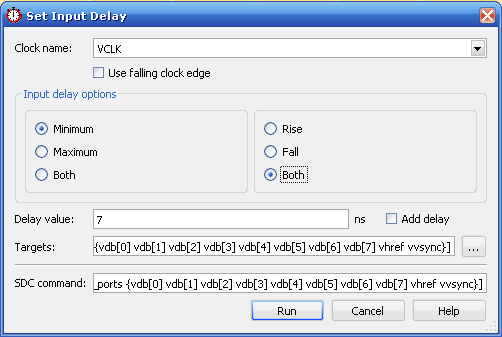

点击ContraintsàSet Minimum Delay,对vdb[0] vdb[1] vdb[2] vdb[3] vdb[4] vdb[5] vdb[6] vdb[7] vhref的set_min_delay做如下设置。

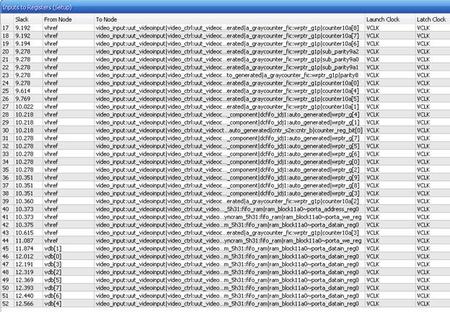

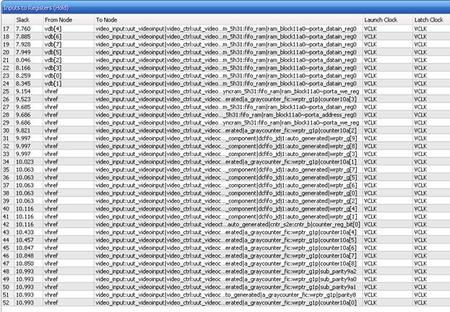

约束完成后,参照前面章节Update Timing Netlist并且Write SDC File…,接着就可以重新编译整个工程,再来看看这个时序分析的报告。在报告中,数据的建立时间有9-13ns的余量,而保持时间也都有7-11ns的余量,可谓余量充足。

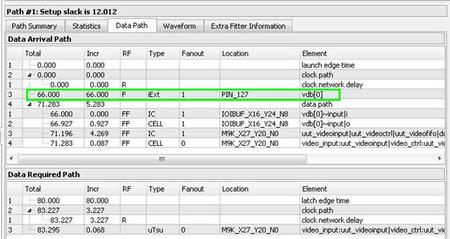

另外,我们也可以专门找一条路径出来,看看它的具体时序路径的分析。vd[0]这条数据线的建立时间报告中,66ns的input max delay出现在了Data Arrival Path中。

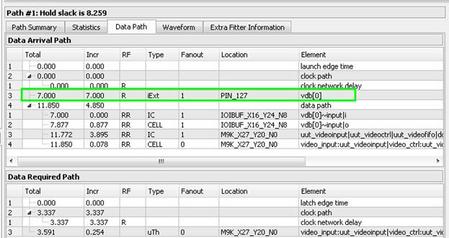

而在vd[0]的保持时间报告中,7ns的input min delay则出现在了Data Arrival Path中。

详细的文档请参考:

http://group.ednchina.com/GROUP_GRO_14596_1375.HTM

SF-CY3/SF-SENSOR/SF-LCD开发套件:http://myfpga.taobao.com/

/5

/5

用户377235 2013-6-3 20:55

你好,请问通过那些具体步骤操作可以看到registers to outputs(setup)这个窗口?