标签: 晶振阻抗

标签: 晶振阻抗

相关博文

-

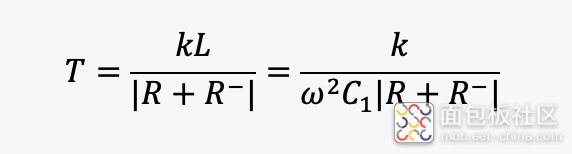

在晶振电路设计中,近端和远端的相位噪声会受到不同因素的影响。通常,晶振的近端相噪主要由晶体自身的参数决定,而远端相噪则更多地依赖于晶体匹配的振荡IC的特性。电性能参数,如起振时间、负载电容、负性阻抗,都对近端和远端相位噪声都有重要影响。 KOAN凯擎小妹建议优先确保近端的稳定性,同时通过适当减少晶体电流和负载电容来改善近端相噪。另外,通过增加电流可以优化远端的相噪表现。在设计晶振电路时,建议根据应用需求在相噪、起振时间和负载电容之间进行合理权衡,以优化电路性能。 1. 起振时间(T) 起振时间的长短主要由晶体的谐振电阻和振荡器的负性阻抗共同决定。高Q值的晶体谐振电阻较小,因此起振速度更快。公式如下, 其中谐振电阻R,负电阻Rˉ、动态电感L、动态电容C1、频率ω、k为常数(12~30): 2. 负性阻抗(Rˉ) KOAN振荡器的负性阻抗通常设计为晶体谐振电阻的3至20倍,这样可以有效加快起振过程并提高振荡的稳定性。负性阻抗的倍数越高,起振速度越快。 其中:gm为跨导,与振荡IC的设计相关。在负载电容CL较小的情况下,增加 gm的值可以提高负性阻抗,从而加快起振。 3. 负载电容(CL) 负载电容的大小不仅影响振荡器的负性阻抗,还会对近端和远端相噪带来不同的影响: 小的CL :较小的负载电容使负性阻抗变大,起振速度更快,牵引量更大,但同时也更容易受到杂散电容的影响。这对近端相噪有利,但可能增加远端相噪。 大的CL :较大的负载电容会减小负性阻抗,导致起振速度较慢,但杂散电容的影响较小,有助于提升远端相噪的稳定性,可能对近端相噪不利。

-

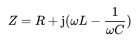

在晶体的两侧施加电压时,晶片就会产生机械振动。在某种频率下,振动的幅度会变大,这叫做压电谐振。 1. 区分电阻和阻抗 电阻(简称R)在电路中限制所在支路的电流大小的元件。晶振的电阻越小越好,如果过大,容易不起振,增加能耗。对晶振来讲,频率越高,晶片越薄,电阻就小。相反,频率低,晶片厚,电阻大。 阻抗(简称Z)对电路中电流其阻碍作用。 实数部分为电阻R,虚数j部分为电抗。电容在电路中对交流电起阻碍作用叫做容抗1/wC;电感起阻碍作用叫做感抗wL。电容和电感总称为 电抗 。 2. 电抗频率曲线 晶体阻抗的斜率表示随着频率的增加,在特定的频率下,串联电容C和电感L之间的作用产生串联谐振电路,将晶体的阻抗降低到最小并等于R并得到串联谐振频率fs。 当频率增加到串联谐振点上时,晶体相当于电感,直到频率达到并联谐振频率fp 时,晶体两端的阻抗达到最大值。 在fs和fp之间,当两个并联电容抵消时,晶体呈现电感性。小于fs或者大于fp时,晶体呈现电容性。 3. 计算晶振的谐振频率fs和fp 假设Rs = 6.4Ω, Cs = 0.09972pF, Ls = 2.546mH,Cp = 28.68pF, 计算晶体fs和fp: 可见fs和fp很相近,差值约为18khz。在这个狭小的频率范围内,晶体为感性,需要在KOAN晶振外部并联合 适的电容,就可以组成并联谐振电路。这个合适的电容就是负载电容。