在晶振电路设计中,近端和远端的相位噪声会受到不同因素的影响。通常,晶振的近端相噪主要由晶体自身的参数决定,而远端相噪则更多地依赖于晶体匹配的振荡IC的特性。电性能参数,如起振时间、负载电容、负性阻抗,都对近端和远端相位噪声都有重要影响。

KOAN凯擎小妹建议优先确保近端的稳定性,同时通过适当减少晶体电流和负载电容来改善近端相噪。另外,通过增加电流可以优化远端的相噪表现。在设计晶振电路时,建议根据应用需求在相噪、起振时间和负载电容之间进行合理权衡,以优化电路性能。

1. 起振时间(T)

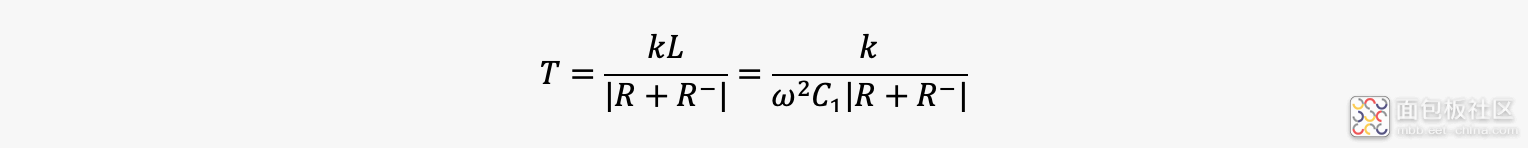

起振时间的长短主要由晶体的谐振电阻和振荡器的负性阻抗共同决定。高Q值的晶体谐振电阻较小,因此起振速度更快。公式如下,其中谐振电阻R,负电阻Rˉ、动态电感L、动态电容C1、频率ω、k为常数(12~30):

2. 负性阻抗(Rˉ)

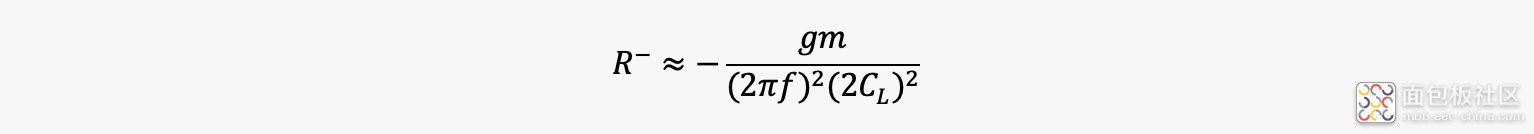

KOAN振荡器的负性阻抗通常设计为晶体谐振电阻的3至20倍,这样可以有效加快起振过程并提高振荡的稳定性。负性阻抗的倍数越高,起振速度越快。其中:gm为跨导,与振荡IC的设计相关。在负载电容CL较小的情况下,增加gm的值可以提高负性阻抗,从而加快起振。

3. 负载电容(CL)

负载电容的大小不仅影响振荡器的负性阻抗,还会对近端和远端相噪带来不同的影响:

作者: koan-xtal, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3907541.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论