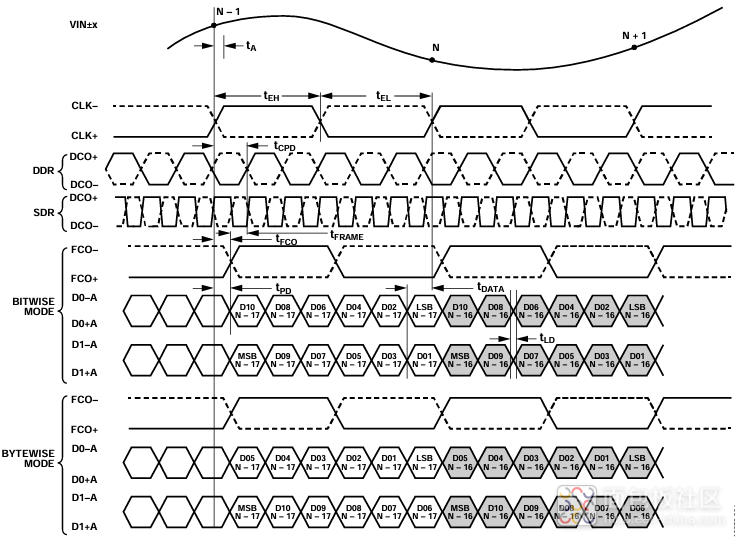

概述 所谓默认情况,即如器件手册中图2所标示那样。对应AD9633的调试,除了涉及到ADC自身,还需要兼顾前端驱动器,系统中AD9633驱动器使用了差分运算放大器,这里不在赘述,笔者已有相关文章论述。 此外,默认情况下的调试,还有一文已经谈及了与FPGA联调时如何让逻辑进行“字”对齐,参考《AD9633在旁路SPI接口时如何出在FPGA逻辑中确认字边界》一文(已更名:AD9633默认情况下调试记录(一))。故本文属于默认调试记录(二)。 AD9633默认工作设置 AD9633是4通道、12位、80/105/125 MSPS高速串行LVDS模数转换器(SST使用100MHz采样率,故选购的芯片为105MSPS即可)。该ADC会自动倍乘采样速率时钟,以便产生合适的LVDS串行数据速率。它提供一个数据时钟输出(DCO)用于在输出端捕获数据,以及一个帧时钟输出(FCO)用于发送新输出字节信号。每一个通道都拥有两组LVDS差分数据线,在默认模式下分别串行传输低数位和高数位数据。图1是AD9633在默认工作模式下的时序图(截取手册中Figure 2): 图1:AD9633默认工作时序图,DDR/SDR,12-bit,双道,x1帧模式 尽管ADI的这类ADC支持单道输出,但是由于采样频率比较高,单道输出串行数据率会超过1Gbps的限制。退而求其次使用双道,这样就需要消耗双倍的FPGA接收LVDS引脚数量。 而ADC的输出双道数据流又有两种模式,如图1所示,分别为BITWISE MODE和BYTEWISE MODE。BITWISE MODE下,双道分别串行传输偶数位和奇数位数据。BYTEWISE MODE下,双道分别串行传输高6-bit和低6-bit。如图2所示,AD9633数据手册中,表21提供片内寄存器21对于串行输出的设定,默认情况下为双道BYTEWISE。用户如果不喜欢这种模式,可以打通器件的SPI通信接口,进行修改配置。 图2:手册表格21显示了AD9633默认输出设定 AD9633默认配置调试遇到的问题 上面介绍了AD9633串行输出的具体模式,到此笔者在调试的时候一开始认为已经认清了该ADC输出的一切面目,然而在FPGA侧对接收数据进行分析时还是遇到了问题,除了上文提到的另一文中,即《默认情况调试记录一》,讨论到的字边界未对齐问题外,还出现了如图3所示的问题。 图3:SignalTap II观测ADC采样后的数字输出 如图3所示,信号源提供了正弦波信号,而AD9633采样出来的只是得到了上半周期。这个问题困扰了我们一段时间,从怀疑信号源输出幅度不够,到怀疑前端驱动器的直流偏置不对等等。把所有想到的可能检查个遍都未能找到问题根源。如图4所示,更改信号源正弦波各种参数,使用单极性、双极性不同频率、幅度,得到不同的正弦波,采样结果都类似。如图5所示,在调整正弦波幅度后,尽管SignalTap II里可以得到完整的正弦波形,但这是在牺牲ADC一半动态范围的情况下得到的。也即ADC仅利用到了图示中上半部分动态范围,下半部分依然被忽视了。 图4:信号源为AD9633提供不同正弦波 图5:调整正弦波幅度后,虽然能观察到完整的波形,但是ADC只有上半部分动态范围 这个问题最终得到解决,只是因为SignalTap II显示问题。因为AD9633默认输出模式是 2的补码 模式,所以正常采样的时候,如果SignalTap II选择的是无符号线显示就会显示如图3或图5那样,如果选择有符号线,则如图6所示。 图6:显示设置成“Signed Line”模式后,ADC完整动态范围可以显现出正弦波完整波形 参考 Quad, 12-Bit, 80 MSPS/105 MSPS/125 MSPS, Serial LVDS 1.8 V ADC Datasheet LVDS SERDES Intel FPGA IP User Guide: Intel Arria 10 and Intel Cyclone 10 Devices.

标签: AD9633

标签: AD9633