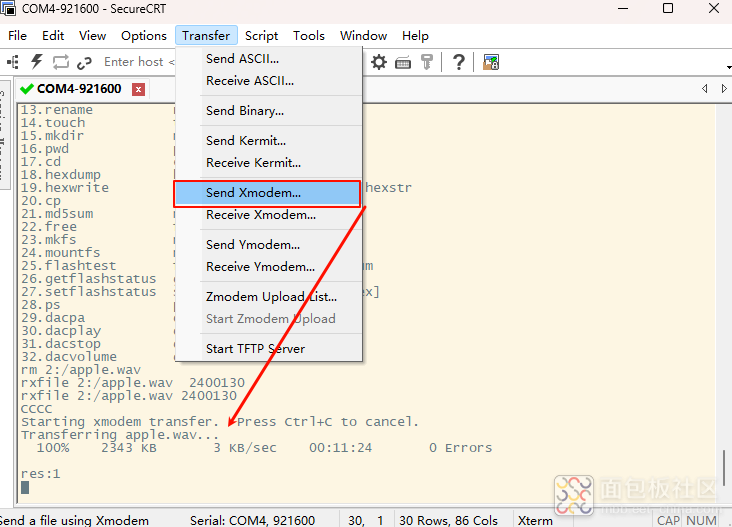

MicroPython 简介 MicroPython 是一个精简且高效的 Python 实现,专为微控制器和嵌入式系统设计。它允许开发者使用 Python 语言在资源受限的硬件(如单片机、开发板等)上编写程序,极大地简化了嵌入式开发的过程。它的特点如下: 1. 特点 轻量化 :MicroPython 的代码库非常紧凑,适合运行在内存和存储空间有限的设备上。 兼容性 :支持大部分 Python 3 的语法和标准库,同时针对嵌入式环境进行了优化。 实时性 :提供了实时操作的功能,适合需要快速响应的应用场景。 硬件交互 :内置对 GPIO、UART、I2C、SPI 等硬件接口的支持,方便直接与硬件通信。 2. 应用场景 MicroPython 常用于以下领域: 物联网 (IoT) :控制传感器、执行器和其他 IoT 设备。 教育 :作为学习嵌入式开发和编程的工具。 原型开发 :快速构建硬件原型,验证概念。 自动化 :实现家庭自动化、工业自动化等应用。 3. 支持的硬件平台 MicroPython 可以运行在多种硬件平台上,包括但不限于: ESP8266 和 ESP32(Wi-Fi 模块) STM32 系列微控制器 Pyboard(官方开发板) Raspberry Pi Pico(RP2040 芯片) 4. 开发工具 WebREPL :通过 Wi-Fi 或串口连接设备,进行远程调试和代码上传。 Thonny :一款简单易用的 IDE,支持 MicroPython 开发。 Mu Editor :专为初学者设计的轻量级编辑器,支持 MicroPython。 VS Code 插件 :Visual Studio Code 提供了丰富的插件来支持 MicroPython 开发。 5. 学习资源 官方文档: https://docs.micropython.org 社区论坛: https://forum.micropython.org GitHub 仓库: https://github.com/micropython/micropython REPL MicroPython 工程 第一次接触MicroPython工程,感觉移植适配到一个新的平台适配工作还是挺大的。当前项目除了需要适配,还需要在 MicroPython 中新增模块,绑定开发板上的硬件播放本地音频文件,至少需要支持SD卡、文件系统、音频播放的硬件(DAC)等等。 这里偷懒,直接使用大佬 qinyunti 的工程,项目地址: https://gitee.com/qinyunti/fr3068-e-c-micropython 工程结构 裁剪了官方的 fr3068-e sdk,只保留了启动文件、驱动、蓝牙驱动、FreeRTOS,删除了 LVGL。 音频播放工程的关键代码都放在了 examples/evb_demo/lvgl_demo/src 目录下: easylogger 日志组件 fr_bt 富芮坤蓝牙应用层 fr_device 板级驱动 py 是MicroPython核心源码 py_port 是针对此款开发板的适配层,并新增了命令 shell 一个命令行组件,开机默认运行这个shell,串口接收命令 硬件环境 完成本次任务需要的硬件环境如下: SD卡,存储音频文件。 喇叭,播放音频 富芮坤 FR3068x-C 开发板,运行 MicroPython 固件 音频文件转换 使用 ffmpeg 工具把 MP3 文件转换为 WAV 文件。 从第15秒钟开始转换音乐文件 ffmpeg/ffmpeg.exe -i apple.mp3 -ac 1 -ar 16000 -acodec pcm_s16le -ss 00:00:15 -t 00:01:15 apple.wav 部分shell命令 传输音频文件 开发板和上位机通过串口传输文件,使用 Xmodem 或者 Ymodem,需要在开发板实现对应的 shell 命令,并支持把文件写入 SD 卡。 开发板shell命令接收音频文件 rxfile filepath filesize filepath 表示文件在SD上的文件路径,例如 2:/apple.wav filesize 表示wav文件的大小,以字节为单位,例如 apple.wav 文件在磁盘的大小为 2400130 字节 例如开发板shell命令中输入 rxfile 2:/apple.wav 2400130 命令,然后在上位机工具通过 Xmodem 发送 apple.wav 文件,如下图所示: 传输完毕,开发板打印 res:1 shell 播放音频 打开功放 dacpa 1 关闭功放 dacpa 0 播放音频 dacplay 2:/apple.wav 停止播放 dacstop 调整音量 dacvolume 20 micropython 播放音频 从shell进入micropython环境,输入命令 micropython。 从 micropython 环境退出,按住 ctrl+d 组合键。 输入以下代码播放音频 python import pyb audio = pyb.AUDIO(1) # 开始播放 audio.play("2:/apple.wav") # 停止播放 audio.stop() # 调节音量 audio.volume(5) # PA 开 audio.mute(0) # PA 关 audio.mute(1) 视频演示

标签: pa

标签: pa