标签: dp

标签: dp

相关帖子

-

发表于 2021-10-19最后回复 TEL13699758578 2021-10-19 10:00浏览2214回复0

相关博文

-

在电子产品发展的过程中,高速接口的演进让消费者在使用上越来越方便,从早期由不同厂商主导的多样化硬件接口,到现在由各个主要协会带领整合所有会员的贡献、制定共同标准,在这些共同标准中又有许多功能可选择性支持,让产品基于不同市场能被弹性应用。下面就让我们来看看高速接口的演进与未来趋势。 » 影音传输接口的演进 早期计算机不普及,显示应用主要在电视接口为模拟讯号的AV端子及S端子,1990年计算机开始发展,计算机屏幕与电视慢慢变成显示市场的两大主流,分辨率提高的要求下由VGA到DVI与HDMI,从模拟转变为数字讯号,而HDMI的发展主要由电视影音相关领域的品牌所主导,一个是连接天线、机顶盒、播放器、或游戏机远距离观看,另一个为连接计算机近距离使用,在功能与要求差异的推动下,2006年VESA提出DisplayPort架构,与HDMI成为屏幕两大主要接口,但HDMI仍旧为电视的主要接口。 DisplayPort 1.3的推出让数据带宽来到的32.4Gbps,也迫使HDMI必须往上增加带宽,支持更高分辨率与更新率,因此在2017年推出HDMI 2.1 (48Gbps);USB-IF以及VESA在取得Intel授权Thunderbolt技术后,在Type C 接口上推出DisplayPort 2.0 (80Gbps) ,最高可支持16K@60Hz,并且可与USB4的数据流同时传输,让DisplayPort在计算机周边广泛被应用,但在电视领域生态链的采用率仍然偏低,主要原因是VESA与HDMI分属不同生态系与组织,背后有不同的大厂支持,已不单纯是技术与功能考虑,而是大厂对于市场的影响力。 图1:影音传输接口的演进 » 传输接口发展 接下来我们从另一个角度来看看技术的演进,由下图可以看出拉高传输速度的领头羊就是PCIe,近20年的电子发展CPU、GPU或各式各样的核心处理器主流都是应用PCIe作为IC对外的主要传输总线,因为IC设计能力提升,加上半导体制程进步使得PCIe1由2.5Gbps per lane到现在PCIe6的64Gbps per lane;但PCB的材质也渐渐地走到了可量产的物理极限,所以在传送端与接收端的补偿机制如Pre-amp、Pre-shoot、amplitude negotiation、CTLE、FFE、DFE等技术的导入都是为了克服PCB板材与Cable线材的损耗。 我们也观察到SATA与SAS这类的储存应用界面正被PCIe直接取代,因为SSD的崛起,架构上让PCIe直通、减少其他IC的桥接、简化设计;加上Thunderbolt、USB、DisplayPort这些界面都融合到Type C上,界面应用的整合虽然对消费者来说是非常方便的,把影像、声音、数据、控制与电源全部整合,但对于IC与产品开发者却要花费更多的资源与时间去验证各式各样排列组合的兼容性,这也是协会与认证实验室的重要性,确保大家有一致性的作法,让成千上万的产品到消费者手上皆能被正常使用。 图2:高速传输接口的演进 谈到接口的未来发展,大家可以想想IEEE802.3,他是网络通讯的基石,技术上是走在高速接口的前端,如下表Ethernet最高已经到112Gb/s,单纯用NRZ架构一次传一个bit已不够用,所以有了PAM架构让数据可以一次传2个bit以上,因为频率已无法再提升,因此只能用电压幅值大小的区别来传送更多数据量,数据协议也不在底层架构下区分,以上特征即是未来接口发展的趋势。上面有提到USB4和DisplayPort 2.0应用到Thunderbolt的技术,如果大家了解Thunderbolt的CIO ( Converged-IO ) Protocol,它早期的传输速度是10.3125 Gb/s与20.625 Gb/s,还有装置识别用相似于IP的概念,没有区分数据型态皆可用Tunneling方式承载,这些都跟Ethernet技术类似。也就是说Data Center的技术应用走得最快但相对成本高,成熟后会应用到消费性电子。 表1 随着云端数据库的蓬勃发展,可以预见大多数终端产品不需具备强大功能,只需注重在输入接收如录像及拍照,还有输出呈现如画面声音播放有足够的处理能力,大量数据储存与运算能力可以藉由Data Center来完成;所以Data center无论有线无线的网络通讯都需要在硬件技术飞速成长,以符合越来越多云端应用以及海量数据的智能运算,因此量子计算机技术的发展以及6G星链的讨论都是为强大的Data Center预做准备,当然,随即延伸而来的资安黑客问题,就是另一个大家关心的话题了。 图3:高速传输接口的演进 作者 GRL大中华区总经理 庄益林 Alan Chuang 具仪器业界超过七年的服务经验,熟悉各传输界面技术与应用,现担任GRL大中华区总经理,负责大陆区与台湾区三个实验室的业务拓展与未来发展目标。

-

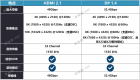

DP1.4 PHY Overview DP1.4 为现行市面上最新、最高画质的显示传输技术,透过 DP1.4 的传输规格,可以输出到最高 7680x4320 @60Hz(8K) 的分辨率。 DisplayPort 的高速讯号为一种单向的传输技术, Source ( 发送端 – 如计算机 ) 会将高速讯号输出到 Sink ( 接收端 – 如屏幕 ) ,以达到高画质的显示。本篇文章将深入浅出的带大家探讨 DP1.4 的物理层 (Physical Layer) 测试,而物理层的测试中,又可分为传送端 (Transmitter - Tx) 与接收端 (Receiver – Rx) 。 DP1.4 Tx Equalizer 在介绍 PHY 的测试前,读者可先了解在 DisplayPort 上会使用到的 Equalizer( 均衡器 ) ,因为 DP1.4 为相当高速的讯号,讯号在传输时免不了有相当程度的损耗,损耗来源可能为电路板上的线路,或是连接的 cable ,为了避免这些损耗导致讯号传送到 Sink 端时无法被识别, DisplayPort 在 Tx 与 Rx 端均设计了不同的加强方式 (EQ) ,在 Tx 端, DP1.4 使用了不同等级的 Swing/Pre-emphasis Level 来加强讯号, Swing 为调整输出讯号振幅, Pre-emphasis 则是对连续讯号的第一个 bit 做预加强,越高的 Pre-emphasis Level 加强的比值越大 ( 第一个 Bit/ 后面连续 Bit)。 Transmitter EQ ( 表一 ) DP1.4 Rx Equalizer 而在接收端方面, DP1.4 则设计了 DFE 以及 10 种不同的 CTLE 来对高速讯号做运算还原, CTLE 为一种针对不同频率的转移函数,此转移函数会将讯号的高频成份放大,低频成份衰减,来达到讯号高低频的均衡,进而使接收端收到的眼图更漂亮。 DP1.4 CTLE (Rx EQ) for HBR3 ( 图一 ) 1. DP1.4 Transmitter (Tx) PHY 在 Tx 讯号测试时,我们会透过 Reference Sink 来与 DUT (Source) 连接,诱使 DUT 进入测试模式,进而改变输出的讯号的种类及参数,包括不同的测试 Pattern , Swing/Pre-emphasis Level , SSC On/Off 等等。 1-1 眼图测试 眼图测试为用来验证讯号质量最基本的方法,一般来说,透过观察讯号眼图的眼宽及眼高,是否触碰到 Eye Mask ,可以了解 Source 产品所输出的讯号是否足以被 Sink 所辩识。以下列出 DP1.4 在不同速度的眼高、眼宽规范 ( 表三 ) ,并以一 HBR3 的眼图为例子 ( 图二 ) 。 ( 表三 ) ( 图二 ) 1-2 Jitter 测试 Jitter( 抖动 ) 为影响讯号质量的最主要原因,其成分又可划分为 Deterministic Jitter-DJ ( 确定性抖动 ) 与 Random Jitter-RJ( 随机抖动 ) ,其中 DJ 又可区分为 SJ 、 DDJ(ISI) 、 BUJ 等等成分而在 DP 的测试中,需进行以下的 Jitter 分析 Random Jitter: 随机抖动,常见的来源有热干扰,环境等不确定的干扰。 Sine Jitter(SJ): 周期性抖动,常见的有电路板上的震荡器,电源等干扰。 ISI: (Inter symbol interference) ,通常讯号走过的路径越长,此干扰越大 Total Jitter(TJ): 以上所有 Jitter 成分加成。 以下列出 DP1.4 在 Total Jitter 的规范 ( 表四 ) 1-3 Spread-spectrum(SSC) 展频测试 为了避免高速讯号集中在某个频段而成为干扰源, DisplayPort 采用了 SSC 的展频技术,将 Data Rate 频率打散。在测试 SSC 时,会针对 SSC 的频率以及大小分别进行量测,以下为 CTS 中规范的标准 。 ( 表五 ) 1-3 VTX 测试 (Swing/ Pre-emphasis Level Test) 此测试旨在验证输出的讯号 Swing 与 Pre-emphasis 加重的比例是否足够 这里使用的是 PLTPAT(Pre-emphasis level test pattern) ,测试时,示波器会将讯号由时域转换为频域,并计算出 Transition Bit ( 转态位 ) 与 Non-Transition Bit ( 非转态位 ) 的比值。 ( 表六 ) 2. DP1.4 Receiver (Rx) PHY 对于接收端 Rx 的测试,我们一样会透过 Reference Source 来与 DUT (Sink) 沟通,诱使 Sink DUT 进入到测试模式。接着,我们会透过 BERT( 误码仪、讯号产生器 ) 将一段充满噪声的讯号 ( 包含, Random Jitter, Sine Jitter, ISI, Crosstalk 等等成分 ) 输入到 Sink 端,确保接收端的 IC 仍可准确的判读讯号的 0 与 1 准位。 那要如何确认接收端 IC 是否有准确判读输入的讯号呢 ? 肉眼辨认是一种方式,观察画面是否有亮线闪烁等。但这对高速讯号来说不够明确,且在 DP 的设计也没有 USB 接口的 Loopback mode 模式。故在进行测试时,我们会透过 DPCD 的读取跟写入,来判断 Sink 端是否有讯号误判的情形发生。 DPCD 全名为 DisplayPort Configuration Data. 它储存在 Sink 的 IC 上,上面会宣告 Sink 的能力 (DP 版本,最大速度,支持几个信道等 ) 同时,也可以在上面写入数值,以进行 Source 及 sink 间的 link training 沟通。 回归正题,在 DPCD 的某个特定地址,会记录 SINK 端此时收到的 Error ,意即我们会在测试时,透过写入 DPCD 告诉 Sink 此时要输入何种测试 pattern, 而当 SINK 比对输入讯号后发现,有不一致的位时便会在 Error Count 的 Register 填入 Error 的数量。 进行 Sink PHY 的测试会有三个步骤,不同的阶段,会需要由 BERT 端输出不同的 Pattern ( 图三 ) 。 1. Frequency Lock : 此阶段会进行传输速度、几个 Lane 的比对。 2. Symbol Lock : 此阶段会进行 EQ 的调整,测试 Pattern 的 Align 。 3. Error count : 最后阶段,进行 Test Pattern 的比对,并记录错误量。 我们会依照 CTS ,在一定的时间内观察 Sink 的“ Error Count ”,以判断测试结果为 Pass or Fail 。 ( 表七 ) ( 图三 ) ( 表七 ) 作者 : GRL 台湾 测试工程师 杨宗霖 Robert Yang 具四年测试经验,熟悉 DisplayPort 、 Thunderbolt 、 HDMI 、 USB 等多种测试规范 。

-

欢迎大家持续关注百佳泰测试实验室, 在上一次的技术解读中,我们讲解了 “ HDMI 2.1 与HDMI1.4线缆差异点 ”、“ gCTS 2.1c 的线缆测项 ”、“ HDMI 2.1 线缆认证流程 ” 、“ HDMI 2.1 线缆测试重点提要 ” 。若大家针对HDMI 2.1专栏有什么疑问,欢迎大家随时留言提问。 本期看点如下: HDMI 2.1 与DisplayPort 1.4技术比较 HDMI 1.4b 线缆与Premium HDMI 线缆测试对比 HDMI 1.4b 线缆与Premium HDMI 线缆重点提要 USB-C 转HDMI Adapter/Dongle认证要点 第四章节知识讲解 HDMI 2.1 与DisplayPort 1.4技术比较 HDMI 1.4b 线缆与Premium HDMI 线缆测试对比 HDMI 1.4b 线缆与Premium HDMI 线缆重点提要 (1) 如果是HDMI Premium Cable, 每一条不管变长或变短, 都需要逐笔送 ATC认证 (如:百佳泰测试实验室; SONY HDMI ATC ) , 不能做Self-Test。 (2) 如果是Cable HDMI1.4b Compliance Test (非Premium Cable test), 原则上线缆没有family model。 同款线缆中(例如: AWG, 线材, 焊接方式, 及包覆方式),请将最长的HDMI线缆一定要送 ATC认证 (如:百佳泰测试实验室 ; SONY HDMI ATC ) , 同款较短线缆 可以做Self-test 提交到协会获HDMI LLC ConfirmationLetter, 也可以送ATC认证;也就是说, 即使是同系列线缆, 所有的model都要做测试并one by one submit(注册)到协会 USB-C转HDMI Adapter/Dongle认证要点 协会有一份Clarification on the Non-Compliant USB Type-C™ Converter Cables for HDMI的通知: (需HDMI会员账号登入) 如果 C 公 to HDMI 母的adapter是把DP信号(Type-C端)转成HDMI信号, 那么C公to HDMI母的dongle可以当作HDMI Source认证. 如果 C 公 to HDMI 公的 Cable 把 DP 信号 (Type-C 端 ) 转成 HDMI 信号 , 依照 HDMI 协会的 ” Clarification on the Non-Compliant USB Type-C Converter Cables for HDMI” 是属于 Convertercable 协会还不能认证 。 如果 USBC (DP ALT-Mode) to HDMI 公 cable, 客户若是出货时一起搭着 DPSource 出货 , 可以当成 Direct Attach Source 取证。 注意 必须要搭着 DPSource 一起出货 ,DPSource 比如是笔记本电脑 , 会配一条 Type-C to HDMI Cable 出货 , 表示它的接口是 USB Type-C™ 。 版权申明:如需转载请注明出处。 HDMI, Premium HDMI Cable & HDMI Logo 是 HDMI Licensing Administrator, Inc. 的注册商标。 下期预告: HDMI 认证测试种类 可认证的产品基本测试项目 HDMI 会员会费 HDMI LA会员申请 HDMI 2.1产品的测试政策是什么?

-

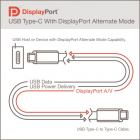

2020年4月29日,DisplayPort&DisplayHDR宣布DisplayPort™ 2.0版代替模式("Alt Mode")标准, 将 DisplayPort2.0性能引入到 USB4™和新的USB TYPE-C® 设备中 。 DisplayPort Alt Mode 2.0版通过USB Type-C连接器启用DisplayPort的所有最新功能,包括超过8K的分辨率和更高的刷新率,以及USB数据传输 。 DisplayPortAlt Mode 2.0 提供了与USB Implementers Forum(USB-IF)发布的新USB4™的无缝互操作性,并通过USB Type-C®(USB-C)连接器完全支持最新版本的DisplayPort标准(2.0版)中的所有功能。 在DisplayPort Alt Mode下,USB-C连接器可以通过电缆中四条高速通道传输高达每秒 80 Gbps 的 DisplayPort视频数据 , 或同时进行高达 40 Gbps 的 超高速USB数据传输 。 DisplayPort&DisplayHDR预计首批采用DisplayPort Alt Mode 2.0的产品 将于2021年上市。

相关资源

-

-

CS5263原理图,CS5263设计电路图,替代IT6563方案设计,DPtoHDMI转换芯片方案设计开发资料

-

-

S7400H与S7300通过DPY-LINK通讯例子

-

-

-

-

ET2OOM,MM42O三个从站上位机和下位机程序,DP和工业以太网通讯2

-

300做主站(含CP343-1),200,ET2OOM,MM42O三个从站上位机和下位机程序,DP和工业以太网通讯

-

CS5218,CS5218原理图,DPtoHDMI,转换器ic,DP转HDMI4K30HZ设计电路参考

-

AIGOLTEKAG7110HDMI&DVI&DP三转一双模开关转换器的中文数据手册.

-

AIGOLTEKAG7110HDMI&DVI&DP三转一双模开关转换器的中文数据手册

-

AIGOLTEKAG7110HDMI&DVI&DP三转一双模开关转换器的中文数据手册

-

AIGOLTEKAG7110HDMI&DVI&DP三转一双模开关转换器的中文数据手册

-

AIGOLTEKAG7110HDMI&DVI&DP三转一双模开关转换器的中文数据手册

-

AIGOLTEKAG7110HDMI&DVI&DP三转一双模开关转换器的中文数据手册

-

介绍了Profibus-DP现场总线的最新发展,并使用Siemens的DP协议芯片SPC3进行了DP总线硬件接口电路的设计,着重介绍了带有DP总线接口的毫伏信号测量智能节点的硬件组成、测量原理及主要程序的流程图。……

-

-

Abstract:Differentialgainandphase(DGandDP)arecommonvideospecifications.Whatarethey?Whyaretheyusediftheycannotbeseen?Thisapplicationnoteanswersthesequestions,andexplainshowthesespecificationsareappliedtoothernonvideoamplifiers,ADCs,andDACs.Maxim>Designsupport>Appnotes>AmplifierandComparatorCircuits>APP4294Maxim>Designsupport>Appnotes>AutomaticTestEquipment(ATE)>APP4294Maxim>Designsupport>Appnotes>Automotive>APP4294Keywords:DG,DP,differentialgainphase,videoerror,NTSC,TV,invisibleamplifier,PAL,subcarrier,ADC,DAC,sweet-spot,linear,linearity,Sallen-Key,filter,video,quality,signalintegrityMay23,2011APPLICATIONNOTE4294DifferentialGainandPhase―WhyMeasureIt,ifYouCannotSeeIt?By:BillLaumeister,StrategicApplicationsEngineerAbstract:Differentialgainandphase(DGandDP)arecommonvideospecifications.Whatarethey?Why……

-

摘要:差分增益和相位(DG和DP)是常见的视频规格。它们是什么?为什么使用它们,如果他们不能看到呢?本应用笔记中回答了这些问题,并解释如何适用于其他nonvideo放大器,模数转换器和数模转换器(DAC),这些规范。Maxim>Designsupport>Appnotes>AmplifierandComparatorCircuits>APP4294Maxim>Designsupport>Appnotes>AutomaticTestEquipment(ATE)>APP4294Maxim>Designsupport>Appnotes>Automotive>APP4294Keywords:DG,DP,differentialgainphase,videoerror,NTSC,TV,invisibleamplifier,PAL,subcarrier,ADC,DAC,sweet-spot,linear,linearity,Sallen-Key,filter,video,quality,signalintegrityMay23,2011APPLICATIONNOTE4294DifferentialGainandPhase―WhyMeasureIt,ifYouCannotSeeIt?By:BillLaumeister,StrategicApplicationsEngineerAbstract:Differentialgainandphase(DGandDP)arecommonvideospecifications.Whatarethey?Why……