DP1.4 PHY Overview

DP1.4 为现行市面上最新、最高画质的显示传输技术,透过DP1.4 的传输规格,可以输出到最高7680x4320 @60Hz(8K) 的分辨率。DisplayPort的高速讯号为一种单向的传输技术,Source (发送端 – 如计算机) 会将高速讯号输出到 Sink (接收端 – 如屏幕),以达到高画质的显示。本篇文章将深入浅出的带大家探讨DP1.4 的物理层(Physical Layer)测试,而物理层的测试中,又可分为传送端 (Transmitter - Tx) 与接收端 (Receiver – Rx)。

DP1.4 Tx Equalizer

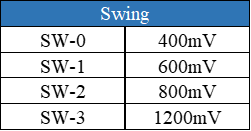

在介绍PHY的测试前,读者可先了解在DisplayPort上会使用到的Equalizer(均衡器),因为DP1.4为相当高速的讯号,讯号在传输时免不了有相当程度的损耗,损耗来源可能为电路板上的线路,或是连接的cable,为了避免这些损耗导致讯号传送到Sink端时无法被识别,DisplayPort在Tx 与 Rx端均设计了不同的加强方式(EQ),在Tx端,DP1.4 使用了不同等级的Swing/Pre-emphasis Level 来加强讯号,Swing 为调整输出讯号振幅,Pre-emphasis 则是对连续讯号的第一个bit做预加强,越高的Pre-emphasis Level加强的比值越大 (第一个Bit/后面连续Bit)。

Transmitter EQ ( 表一 )

DP1.4 Rx Equalizer

而在接收端方面,DP1.4 则设计了DFE以及10种不同的CTLE来对高速讯号做运算还原,CTLE为一种针对不同频率的转移函数,此转移函数会将讯号的高频成份放大,低频成份衰减,来达到讯号高低频的均衡,进而使接收端收到的眼图更漂亮。

DP1.4 CTLE (Rx EQ) for HBR3 ( 图一 )

1. DP1.4 Transmitter (Tx) PHY

在Tx 讯号测试时,我们会透过Reference Sink 来与DUT (Source) 连接,诱使DUT进入测试模式,进而改变输出的讯号的种类及参数,包括不同的测试Pattern,Swing/Pre-emphasis Level,SSC On/Off 等等。

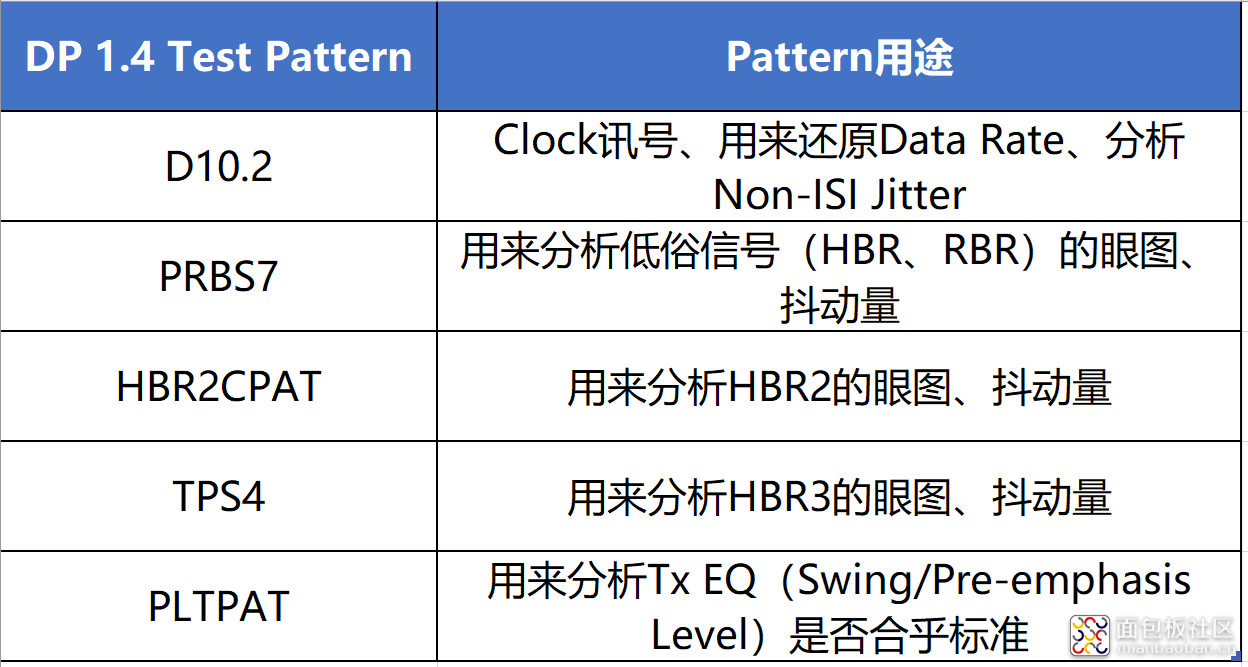

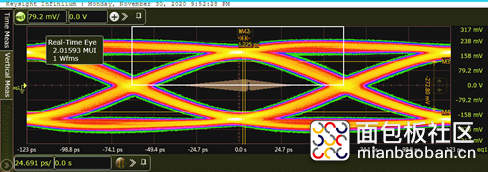

1-1 眼图测试

眼图测试为用来验证讯号质量最基本的方法,一般来说,透过观察讯号眼图的眼宽及眼高,是否触碰到Eye Mask,可以了解Source 产品所输出的讯号是否足以被Sink所辩识。以下列出DP1.4 在不同速度的眼高、眼宽规范(表三),并以一HBR3 的眼图为例子(图二)。

( 表三 )

(图二)

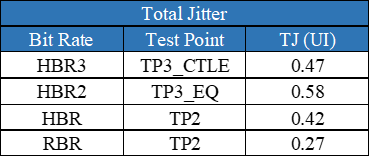

1-2 Jitter测试

Jitter(抖动) 为影响讯号质量的最主要原因,其成分又可划分为Deterministic Jitter-DJ (确定性抖动)与Random Jitter-RJ(随机抖动),其中DJ 又可区分为SJ、 DDJ(ISI) 、BUJ 等等成分而在DP 的测试中,需进行以下的Jitter分析

Random Jitter: 随机抖动,常见的来源有热干扰,环境等不确定的干扰。

Sine Jitter(SJ): 周期性抖动,常见的有电路板上的震荡器,电源等干扰。

ISI: (Inter symbol interference),通常讯号走过的路径越长,此干扰越大

Total Jitter(TJ): 以上所有Jitter成分加成。

以下列出DP1.4 在Total Jitter 的规范

( 表四 )

1-3 Spread-spectrum(SSC) 展频测试

为了避免高速讯号集中在某个频段而成为干扰源,DisplayPort 采用了SSC的展频技术,将Data Rate 频率打散。在测试SSC时,会针对SSC的频率以及大小分别进行量测,以下为CTS中规范的标准 。

( 表五 )

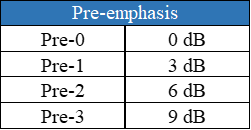

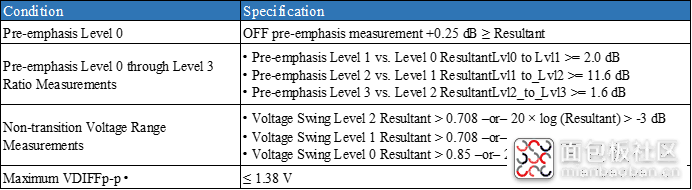

1-3 VTX 测试 (Swing/ Pre-emphasis Level Test)

此测试旨在验证输出的讯号Swing 与 Pre-emphasis加重的比例是否足够

这里使用的是PLTPAT(Pre-emphasis level test pattern),测试时,示波器会将讯号由时域转换为频域,并计算出Transition Bit (转态位)与Non-Transition Bit (非转态位) 的比值。

(表六)

2. DP1.4 Receiver (Rx) PHY

对于接收端Rx 的测试,我们一样会透过Reference Source 来与DUT (Sink) 沟通,诱使Sink DUT进入到测试模式。接着,我们会透过BERT(误码仪、讯号产生器)将一段充满噪声的讯号(包含,Random Jitter, Sine Jitter, ISI, Crosstalk 等等成分)输入到Sink端,确保接收端的IC 仍可准确的判读讯号的0与1准位。

那要如何确认接收端IC是否有准确判读输入的讯号呢?

肉眼辨认是一种方式,观察画面是否有亮线闪烁等。但这对高速讯号来说不够明确,且在DP的设计也没有USB接口的Loopback mode模式。故在进行测试时,我们会透过DPCD的读取跟写入,来判断Sink端是否有讯号误判的情形发生。DPCD全名为DisplayPort Configuration Data. 它储存在Sink的 IC上,上面会宣告Sink的能力(DP版本,最大速度,支持几个信道等)同时,也可以在上面写入数值,以进行Source及sink间的link training 沟通。

回归正题,在DPCD的某个特定地址,会记录SINK端此时收到的Error,意即我们会在测试时,透过写入DPCD 告诉Sink此时要输入何种测试pattern, 而当SINK 比对输入讯号后发现,有不一致的位时便会在Error Count 的Register 填入Error的数量。

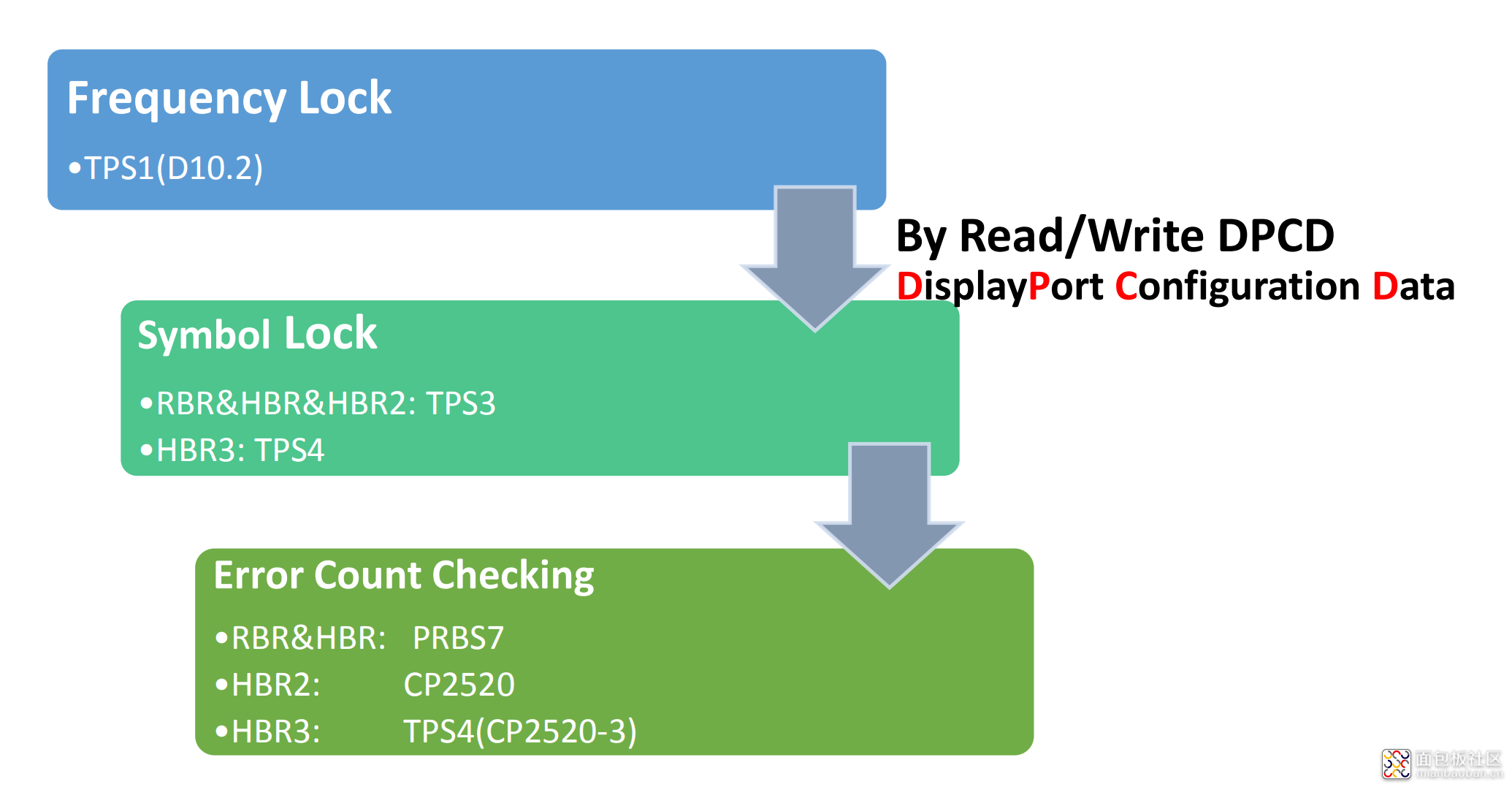

进行Sink PHY的测试会有三个步骤,不同的阶段,会需要由BERT端输出不同的Pattern (图三)。

1. Frequency Lock : 此阶段会进行传输速度、几个Lane的比对。

2. Symbol Lock : 此阶段会进行EQ 的调整,测试Pattern的Align。

3. Error count : 最后阶段,进行Test Pattern 的比对,并记录错误量。

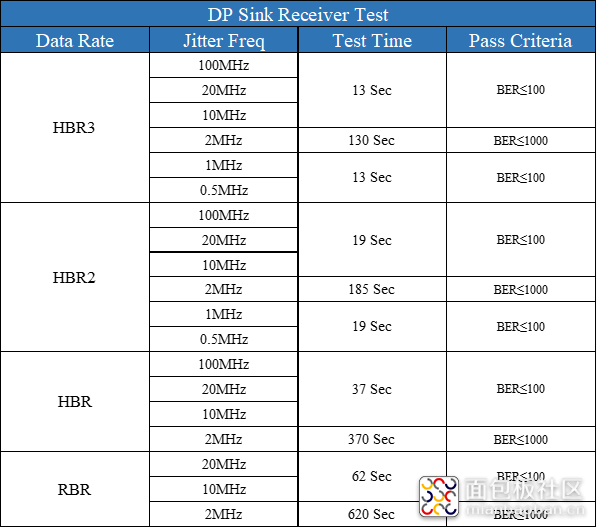

我们会依照CTS,在一定的时间内观察Sink的“Error Count”,以判断测试结果为Pass or Fail。(表七)

(图三)

(表七)

作者:

GRL台湾 测试工程师 杨宗霖Robert Yang

具四年测试经验,熟悉DisplayPort、Thunderbolt、HDMI、USB 等多种测试规范。

作者: GRL实验室, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3943047.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

curton 2021-2-24 21:12