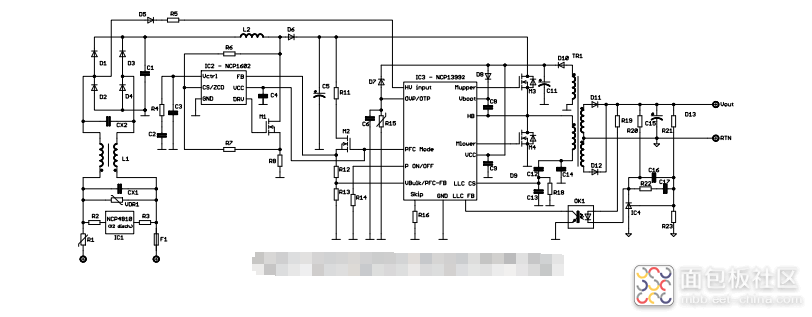

体积大小:14*11*2.6CM,电气参数:输入100V-240V/10A,输出16V24A。 PCB 正面如下图。 PCB 背面如下图。 根据实际功能可以将PCB分成几部分:EMI滤波,PFC电路,LLC电路。 EMI滤波区域,两级共模电感,LN各用了保险丝加压敏电阻,继电器(HF32FV-G)用来切除NTC的,为了提高效率点,如下图。 PFC电路区域,如下图。 LLC电路区域,如下图。 详细分析一下该电源用的主要IC还有功率器件。 AC侧采用了两颗整流桥进行并联,器件增加电流应力,如下图。 共模电感都有放电针,倒三角的裸露PCB部分,ESD时给其放电的,如下图。 PN8201, X电容放电专用芯片,如下图。 NCP1618A,PFC(功率因数校正),用于调整交流电路中的电压和电流之间的相位角,使之趋近于零的半导体器件,如下图。 NCP1618A的 Internal Circuit Architecture,如下图。 NCP1618A的 PIN FUNCTION DESCRIPTION,如下图。 WNSC 10650T(Silicon Carbide Schottky diode),两颗并联,如下图。 WNSC 10650T的规格书,如下图。 NCP13992AX,是一款高性能电流模式控制器,用于半桥谐振变换器。 这款控制器实现了 600 V 栅极驱动器,简化了布局并降低了外部元件数量。 内置掉电输入功能简化了控制器在所有应用中的实现,如下图。 NCP13992AX的 Internal Circuit Architecture,如下图。 NCP13992AX的 PIN FUNCTION DESCRIPTION,如下图。 LLC的原边主功率管,半桥拓扑,如下图。 LLC的副边整流管,两路输出的全波整流,一路用两颗并联,如下图。 SFS06R03G,Rectifier Diode, 1 Element, 3A, 800V V(RRM),如下图。 SFS06R03G数据手册,如下图。 LLC的输出环路反馈板,输出的各种保护通过该板反馈给原边IC,如下图。 4颗光耦芯片,内侧两颗和外侧两颗,用于采集二次侧的信号并反馈给原边的控制IC,光耦隔离有利于电气安全,如下图。 这款开关电源的电路原理图,如下图。 电源的外壳并不是完全封闭的,输出端采用的镂空设计,风扇不转的时候保证了轻负载时的自然散热,如下图。 43080A PFLG稳压器, C58NQ未知,可能是驱动风扇用的,如下图。 DC12V0.3A风扇,如下图。 AC输入L和N的对地Y电容,共地接在了外壳上,如下图。 AC输入L和N的对地Y电容,共地接在了DC输出电容的负极上,如下图。 一次侧接在母线电容的负极,二次侧接在DC输出电容的负极,跨接在热地和冷地之间,有利于电气安全的,如下图。 这款开关电源散热如何处理的,如下图。 风扇是用来抽电源壳里气流的,位于PFC电路的原边功率管和PFC变压器的上方,起到风冷降温的效果,如下图。 风扇的扇叶做的很特别,抽风的频率是很快的,如上图。 整流桥散热器,PFC原边功率管(两颗MOS并联)散热器,LLC谐振电感变压器,LLC主变压器,LLC副边功率管都有贴硅胶垫,增强散热并把热量通过外壳导热到壳外,起到更好的散热效果,如下图。 这款开关电源整体做工还是相当不错的,用料充足,电气安全放在了首位,而且认证了6家的安规认证的,如下图。

标签: llc

标签: llc