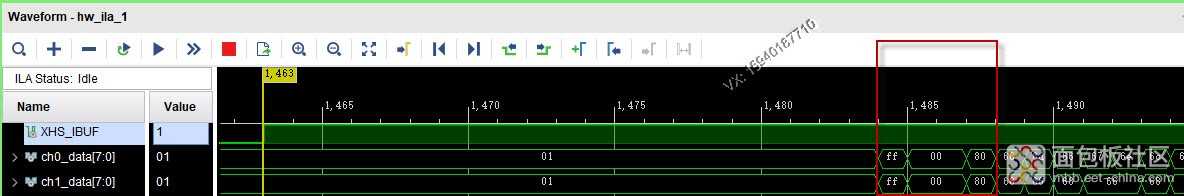

一、摄像头子板简单介绍 摄像头IMX273和IMX287是两个非常相似的SENSOR,均为全局快门和Sub-Lvds接口。这两种摄像头可以共用一块PCB设计(PCB设计的是8LANE数据差分线),根据需要焊接不同的SENSOR就行。摄像头电路板如下: 两个芯片的差异主要如下: 1、分辨率不同。IMX287的分辨率为728*544,有效像素为0.4M;IMX273的分辨率是1456*1088,有效像素为1.58M; 2、帧率不同。IMX287的帧率为52FPS,IMX273的帧率为276FPS; 3、数据传输通道数不同。IMX287的LANE数量为4,IMX273的LANE数量为8; 4、供电电压种类完全相同,共需要三种电压,1.2V、1.8V和3.3V。其中1.8V是接口电路相关电压。 二、Sub-Lvds接口物理电平介绍 1、关于供电电压。Sub-LVDS接口的供电电压通常为1.8V,前面摄像头子板上的1.8V就是供接口电路的电压。FPGA电路板上的BANK34连接到摄像头,BANK34的供电电压也为1.8V。LVDS接口的供电电压一般为5V。 2、关于共模电压。Sub-LVDS的共模电压0.9 V,而LVDS的共模电压为1.25V。 3、关于差分摆幅。Sub-LVDS有更低的差分摆幅150 mV(1.5mA恒流驱动100R),相比LVDS的350 mV(3.5mA恒流驱动100R)。 基于以上的分析,结合ARTIX7的数据手册,A7的FPGA是可以解码出Sub-LVDS信号的。摄像头子板和FPGA开发板相连的图片如下: 三、关于I2C信号 1、IMX287既支持SPI配置,也支持I2C配置,摄像头子板设计时选择的是I2C信号。I2C的设备地址是0x6C/0x6D,寄存器地址是双字节,寄存器的值是单字节。电路板上预留了I2C的两个测试点,方便逻辑分析仪抓取I2C信号。I2C的MASTER既可以用USB3芯片,也可以用FPGA芯片来实现。因为刚开始对IMX273进行I2C读写,可以简单的用USB3芯片的控制传输指令来实现。只有基本的I2C读写成功之后,然后才能一次性写进几十条的I2C配置指令,摄像头才进入指定的正常工作状态,最后才是用FPGA解码。 2、先设定读回寄存器3000位置的值,查手册了解这个寄存器是摄像头启停的控制寄存器,最低位有效,IMX273上电后默认状态是待机状态(默认最低位是1)。寄存器3000具体含义如下: 3、用逻辑分析仪监测I2C总线上的数据如下, 可见读回的值是01,完全正确,验证了硬件电路板是没有问题的。 以上是第一步,读回寄存器地址3000的上电默认值。第二步是向3000写入新值,再读回。自定义USB3的控制传输指令为B0,寄存器地址通过wValue输入,寄存器的值通过wIndex输入,单字节,wIndex低字节有效操作如下: 4、一次性写入I2C配置参数。单个I2C指令测试成功后,FPGA程序需要一次性写入50多条I2C指令,摄像头才能工作在指定的格式下,如外部输入给IMX273的晶振时钟频率是54M的,还是74.25M的;数据LANE数量是4LANE的还是8LANE的;像素点格式是8位的还是10的。我是用FPGA程序实现I2C MASTER的,或者可以用USB3下发I2C指令的。摄像头正常工作后,可以简单用示波器测量一下摄像头电路板上的XHS和XVS行场信号,确认摄像头工作在需要的状态中。 四、基于FPGA的Sub-Lvds解码程序 1、可以直接用SelectIO IP来解码,具体如下: 我也是参考了XILINX的 文档XAPP582的P10,结论是:When the FPGA is used as a receiver of SubLVDS, LVDS_25 or DIFF_HSTL_II_18 can be used as a receiver with a 100Ω parallel termination on the board。当然电平标准不是唯一的。 2、摄像头信号经过SelectIO IP,还要经过BITSLIP的操作,然后可以监测到真正的行头行尾等同步码。关于同步码,可以参考IMX273芯片的数据手册,如下: 每一行开始的有效数据有同步码SAV(Start of ActiveVideo),每一行有效数据结束的有同步码EAV(End of ActiveVideo)。相应的,每一行的无效数据也有SAV和EAV(场消隐)。这四种同步码如下: 同步码共有4上,如果简单的按一个像素点8bit的话,这4个同步码分别是FF 00 00 80、FF 00 00 9D、FF 00 00 AB和FF 00 00 B6。这4种同步码前3个字节都相同,都是FF 00 00,仅是第4个字节不同。同步码的FF和00,不同于图像的有效数据(有效值是01到FE)。同步码和行有效信号XHS的关系如下: 3、ILA中的同步码。同步码很好监测,添加到ILA中就可以,如下是行开始的同步码FF 00 00 80, 如下是行结束的同步码FF 00 00 9D, 接下一回分解。 良子USB,20250405 专注USB3.0、FPGA、PCIE、定制UVC摄像头 VX:15940187710

标签: fpga

标签: fpga