原创

4K视频为何越来越糊?米尔电子MPSOC如何实现SGMII与HEVC重拾高码流体验

1. 引言

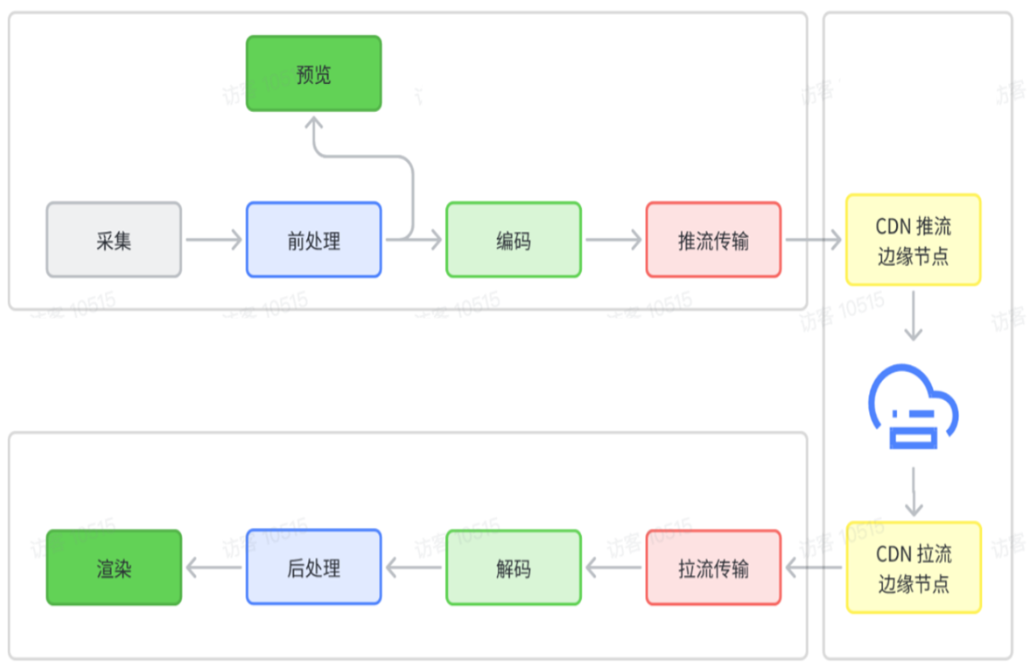

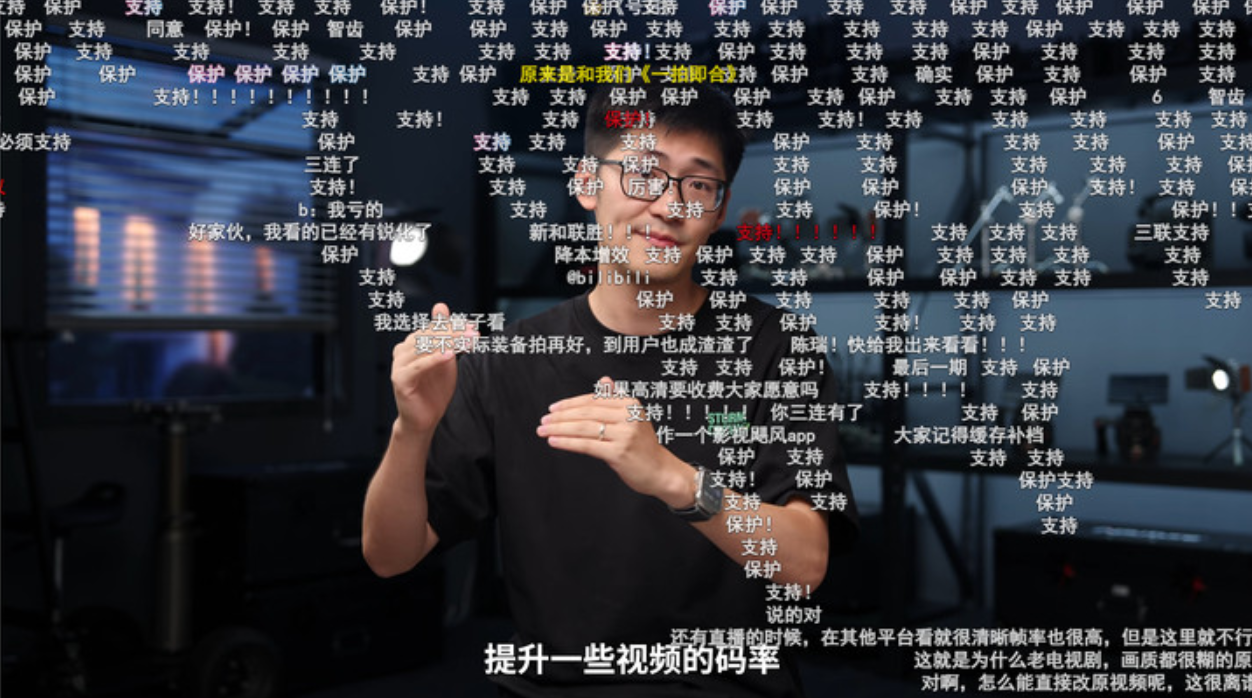

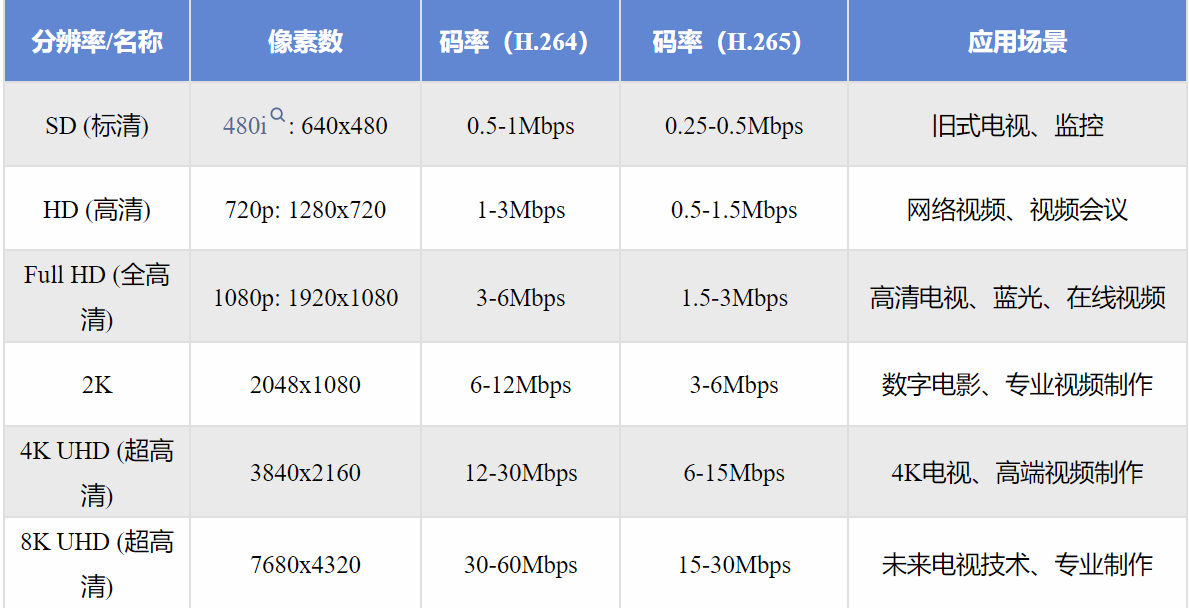

随着网络视频平台的发展,用户对于4K高清画质的需求日益增长。然而,许多用户发现,即使购买了视频平台的会员,观看4K内容时画质却不如预期,有时甚至还会出现模糊、卡顿的情况。这种现象背后涉及到视频编码、网络带宽、和视频传输的诸多因素。

近期“影视飓风”发布的视频《清晰度不如4年前!视频变糊是你的错觉吗?》因讨论视频平台降低码率和改变编码格式以压缩视频画质,影响了内容表达。

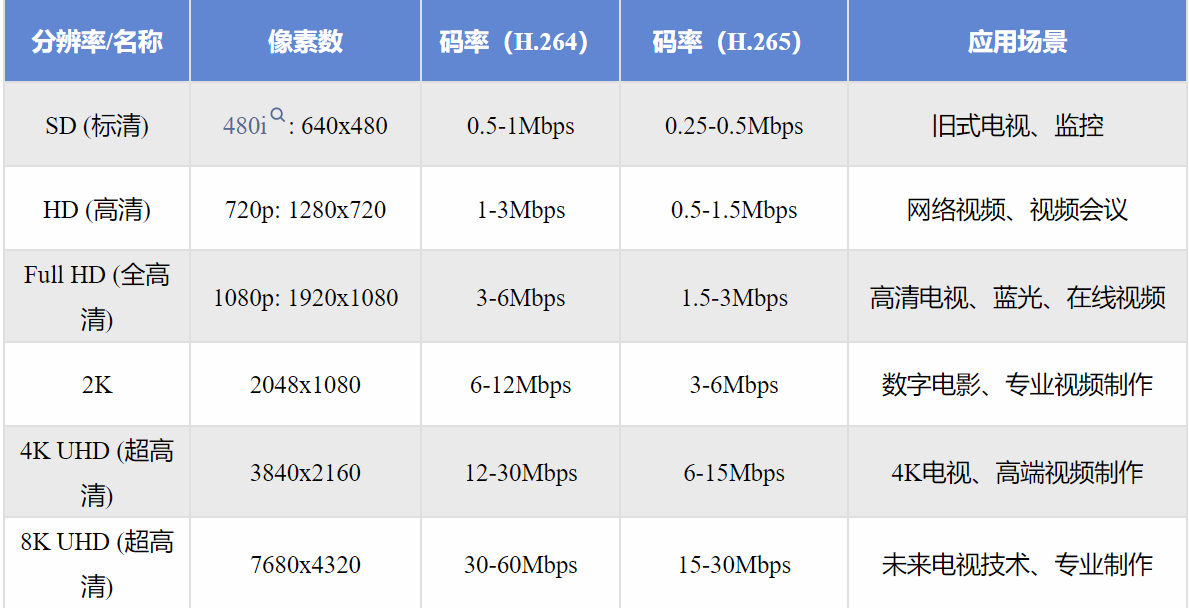

4K视频清晰度下降的一个主要原因是平台为了节省带宽而压缩视频流,有时导致比特率降低,无法发挥4K分辨率的全部潜力。

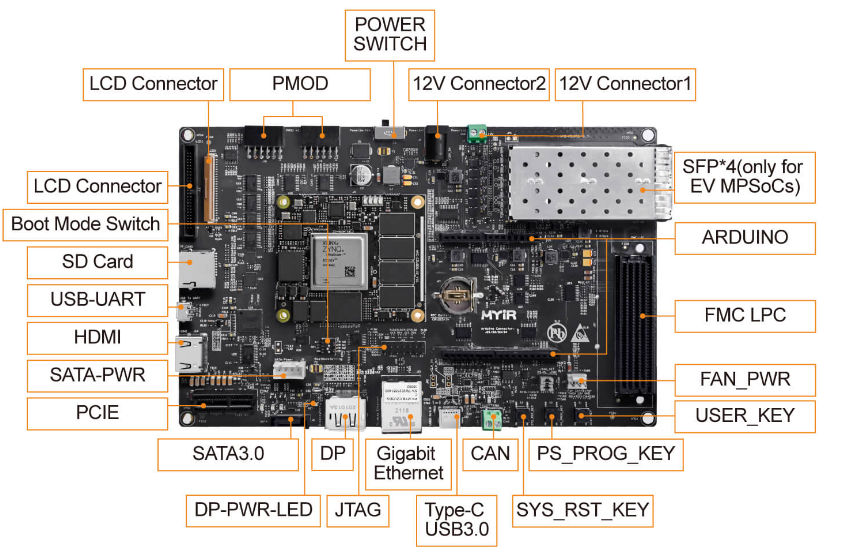

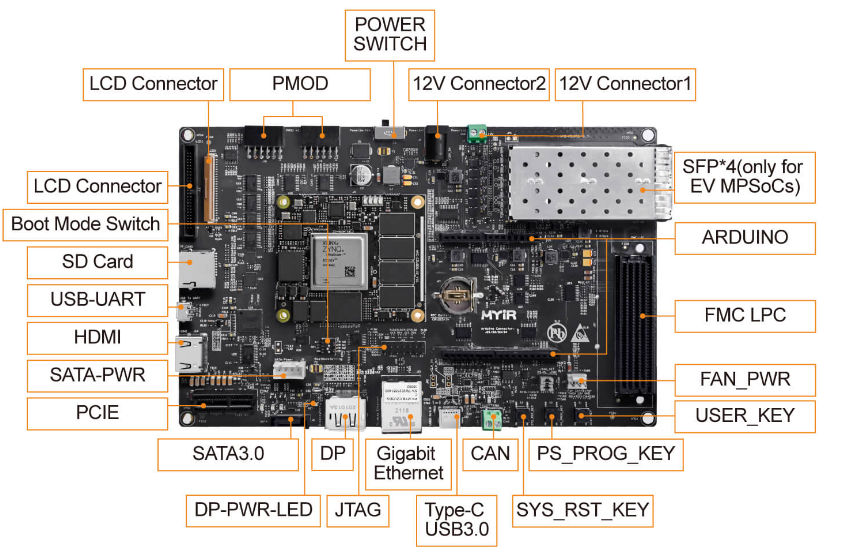

在这种背景下,如何高效地压缩和传输4K视频成为了一个关键技术难题。本文将探讨如何通过米尔电子的ZU4EV MPSoC平台,接入真4k 60UHD-SDI视频源后,使用VCU进行高效H.265编解码,再通过SGMII万兆以太网实现网络推流,以确保高质量4K视频的流畅传输。

2. 视频质量下降的原因与优化方法

1)带宽瓶颈:在用户数量增加的情况下,服务器和网络的带宽常常无法满足4K视频流的需求。

2)压缩算法不足:传统的视频压缩技术在高分辨率内容上表现不佳,容易导致画面模糊。

3)视频流传输的优化在推流过程中,网络带宽和视频压缩效率直接决定了视频播放的清晰度与流畅度。为了确保4K视频在万兆以太网上的高效传输,本设计采用以下优化措施:

- 合理的码率控制:在保证视频清晰度的前提下,调整H.265编码的目标码率,避免过低的码率影响视频质量或过高的码率导致带宽浪费或。通过CBR或VBR模式可以根据网络情况动态调整码率。

- 低延时模式:VCU支持低延时编码模式,确保视频在压缩和传输过程中保持尽可能低的延迟,提升用户的观看体验。

- 网络传输协议选择:根据应用场景选择合适的传输协议。对于实时性要求较高的场景,可选择UDP传输,而对于数据可靠性要求较高的场景,则推荐使用TCP协议。

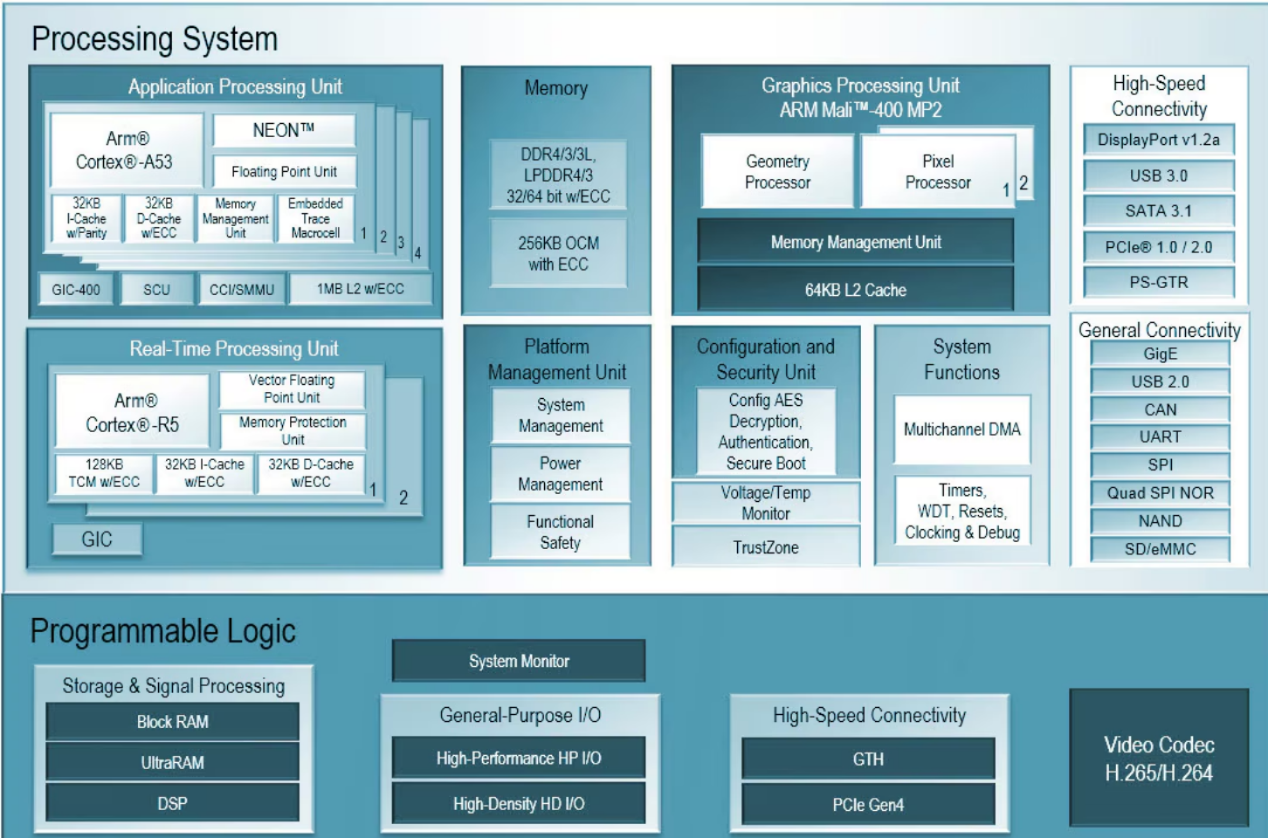

3. MPSoC与VCU架构在4K UHD音视频广播领域的优势

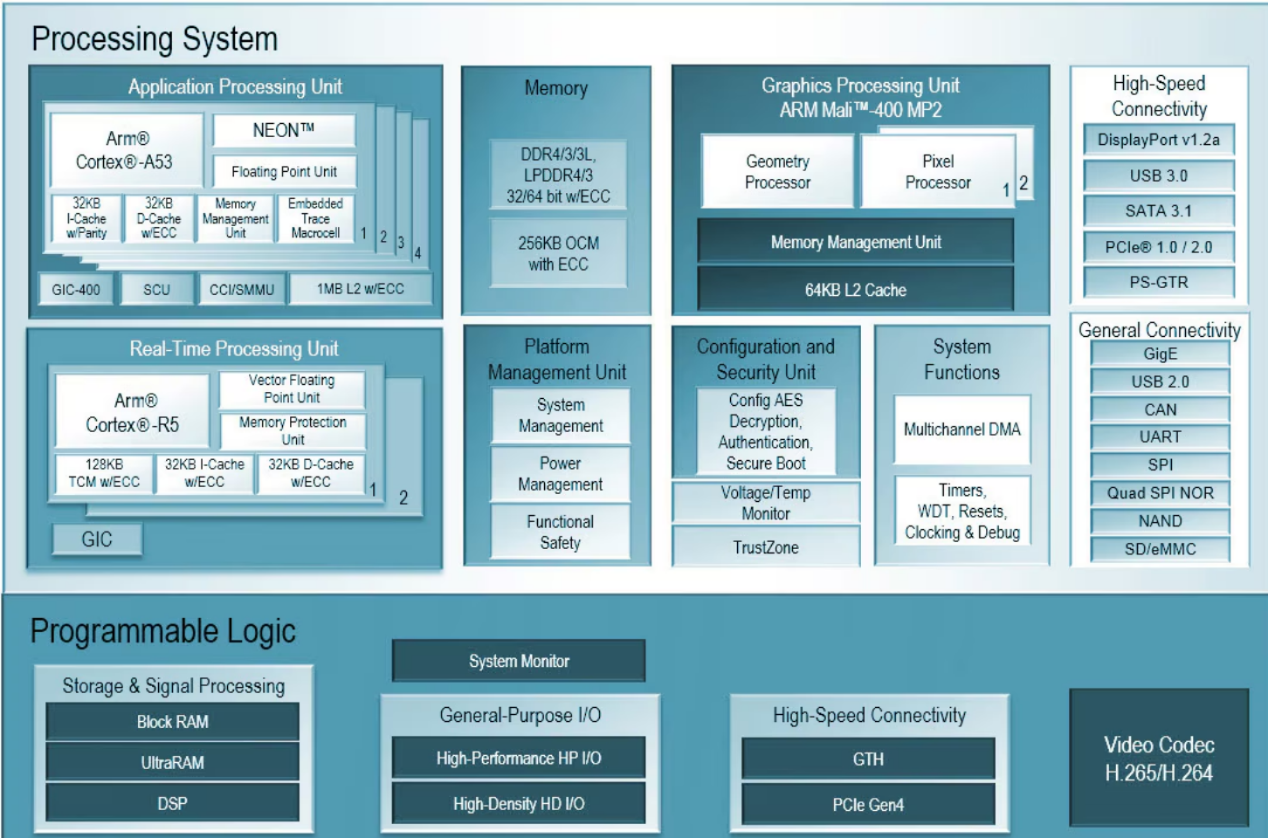

1.高性能与低功耗的结合:Zynq UltraScale+ MPSoC采用了16nm FinFET工艺,集成了多核处理器和可编程逻辑,能够在提高性能的同时降低功耗,这对于音视频广播领域来说至关重要,因为它可以在保证高清晰度视频传输的同时,减少能源消耗。2.实时压缩与解压缩能力:集成的VCU支持H.264/AVC和H.265/HEVC标准,能够实现高达4K UHD分辨率的视频的实时压缩和解压缩。这意味着在广播应用中,可以利用VCU进行高效的视频编码,减少存储空间和带宽的需求,同时保持视频质量。3.多视频流处理能力:VCU能够同时处理多达八个不同的视频流,这对于需要同时广播多个视频源的4K UHD广播应用来说非常有用。这种多任务处理能力使得MPSoC成为多媒体中心和视频服务器的理想选择。4.灵活性和可扩展性:MPSoC的可编程逻辑(PL)提供了任意到任意高速视频/音频接口的灵活性,可以为多媒体管道带来定制图像及视频处理功能的差异化效果。这种可编程性使得系统能够适应不断变化的音视频广播需求。5.专用硬件加速:MPSoC提供了专用的处理引擎,如基于ARM Cortex A53的APU、Mali图形处理单元等,这些专用硬件能够加速图形和视频处理任务,提高系统的整体性能。

6.支持多种视频格式:VCU支持高达4:2:2 10位UHD-4K的视频格式,适合专业和高端消费级的制作与后期制作解决方案。这种广泛的格式支持使得MPSoC可以应用于各种不同的音视频广播场景。

7.集成的多媒体框架支持:MPSoC结合常见的多媒体框架GStreamer,可以开发硬件加速型多媒体应用。这种集成支持简化了开发过程,使得开发者能够快速实现复杂的音视频处理任务。8.优化的功耗管理:Zynq UltraScale+ MPSoC将处理引擎、硬件编解码器等组件放置在具有独立电轨的不同电源域中,这种配置可用于为整个系统设计优化功耗管理方案,进一步降低系统功耗。9.高速互联外设:MPSoC提供高速互联外设,如集成式DisplayPort接口模块,支持高达6 Gb/s的工作速率,这有助于处理来自PS或PL的实时音视频流,进一步降低系统BOM成本。10.支持新一代地面数字电视广播技术:随着超高清电视时代的到来,MPSoC与VCU架构能够支持新一代地面数字电视广播技术,如DVB-T2、ATSC 3.0和DTMB-A等,这些技术支持更高的视频质量和新的广播应用模式。综上所述,MPSoC与VCU架构在4K UHD音视频广播领域提供了高性能、低功耗、实时压缩解压缩、多视频流处理、灵活性、硬件加速、广泛格式支持、多媒体框架集成、优化的功耗管理和高速互联外设等多重优势,使其成为该领域理想的解决方案。

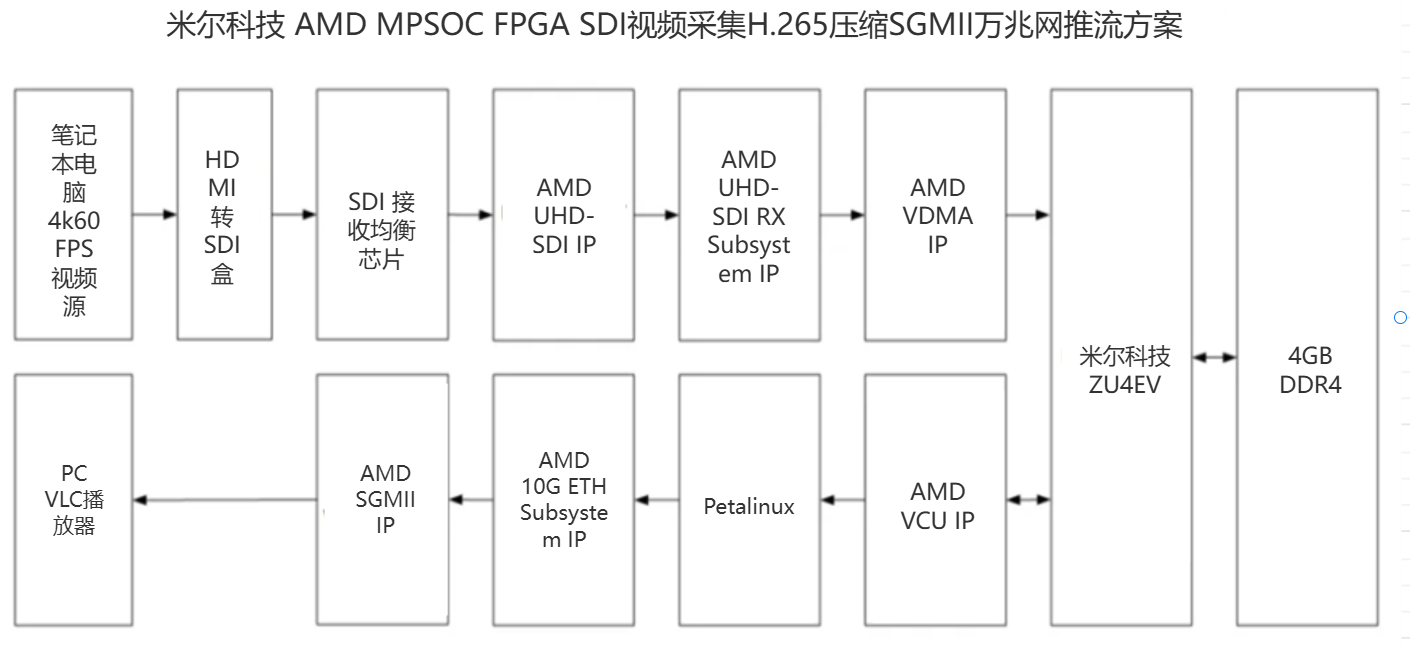

4. 系统架构概述

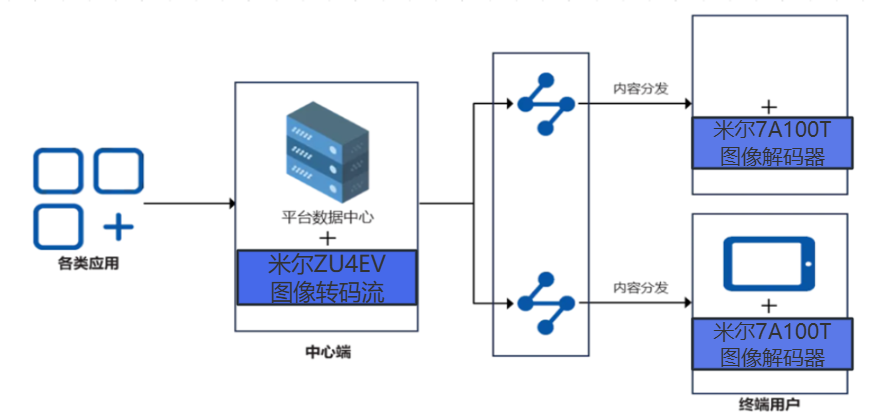

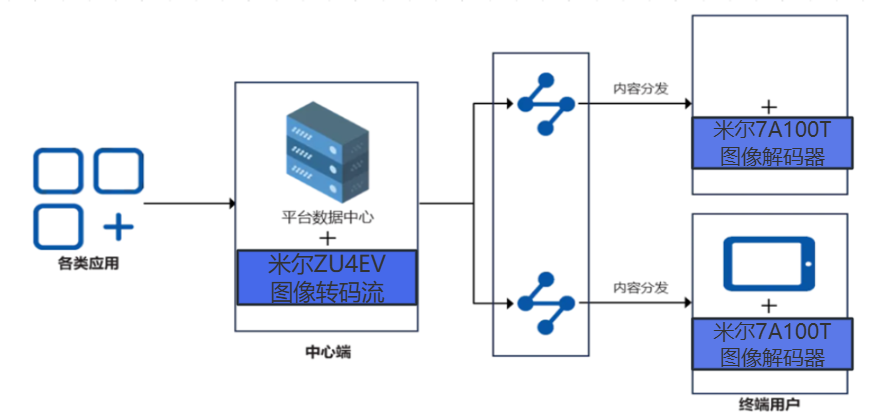

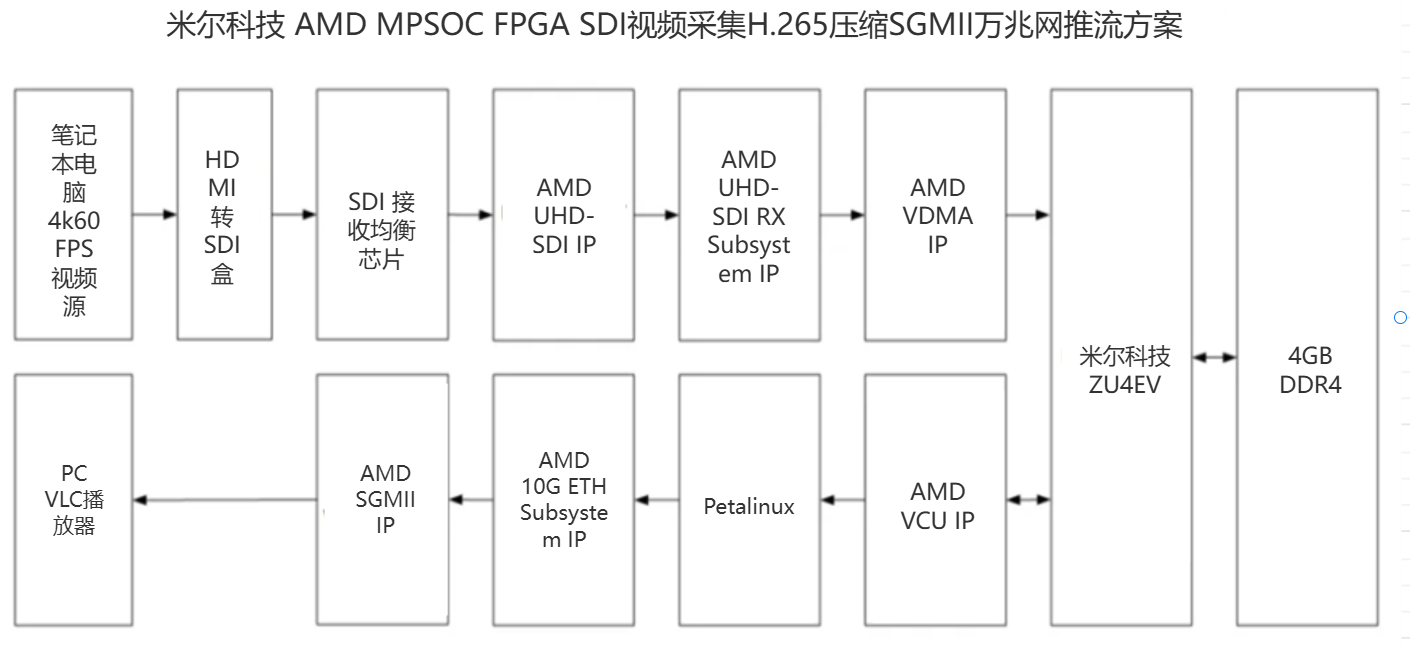

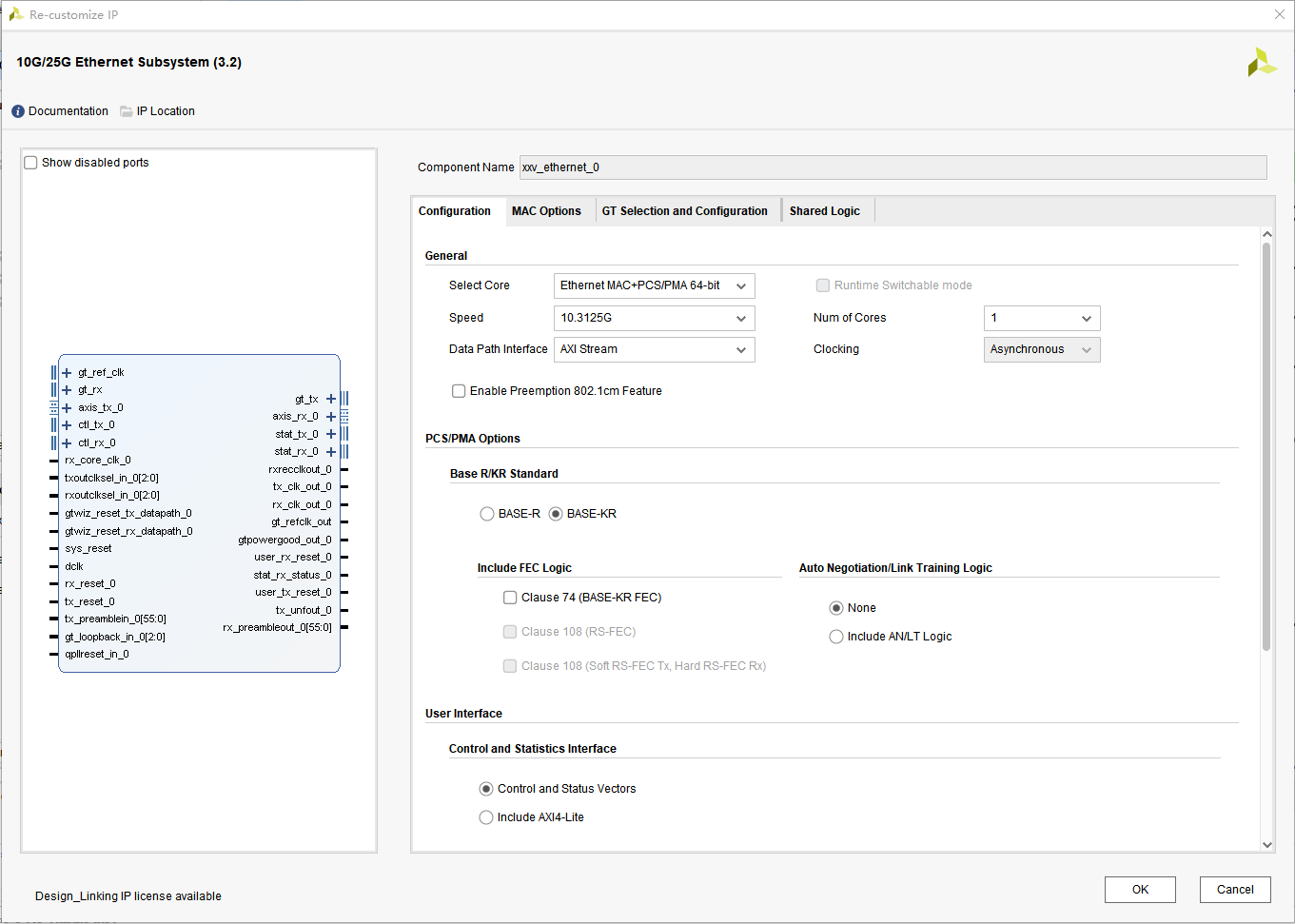

在本设计中,我们使用Zynq UltraScale+ MPSoC平台(具体型号为MYIR XCZU4EV),通过FPGA实现对SDI视频的H265压缩,并通过SGMII接口推送到万兆以太网上。系统架构主要包括以下几个部分:

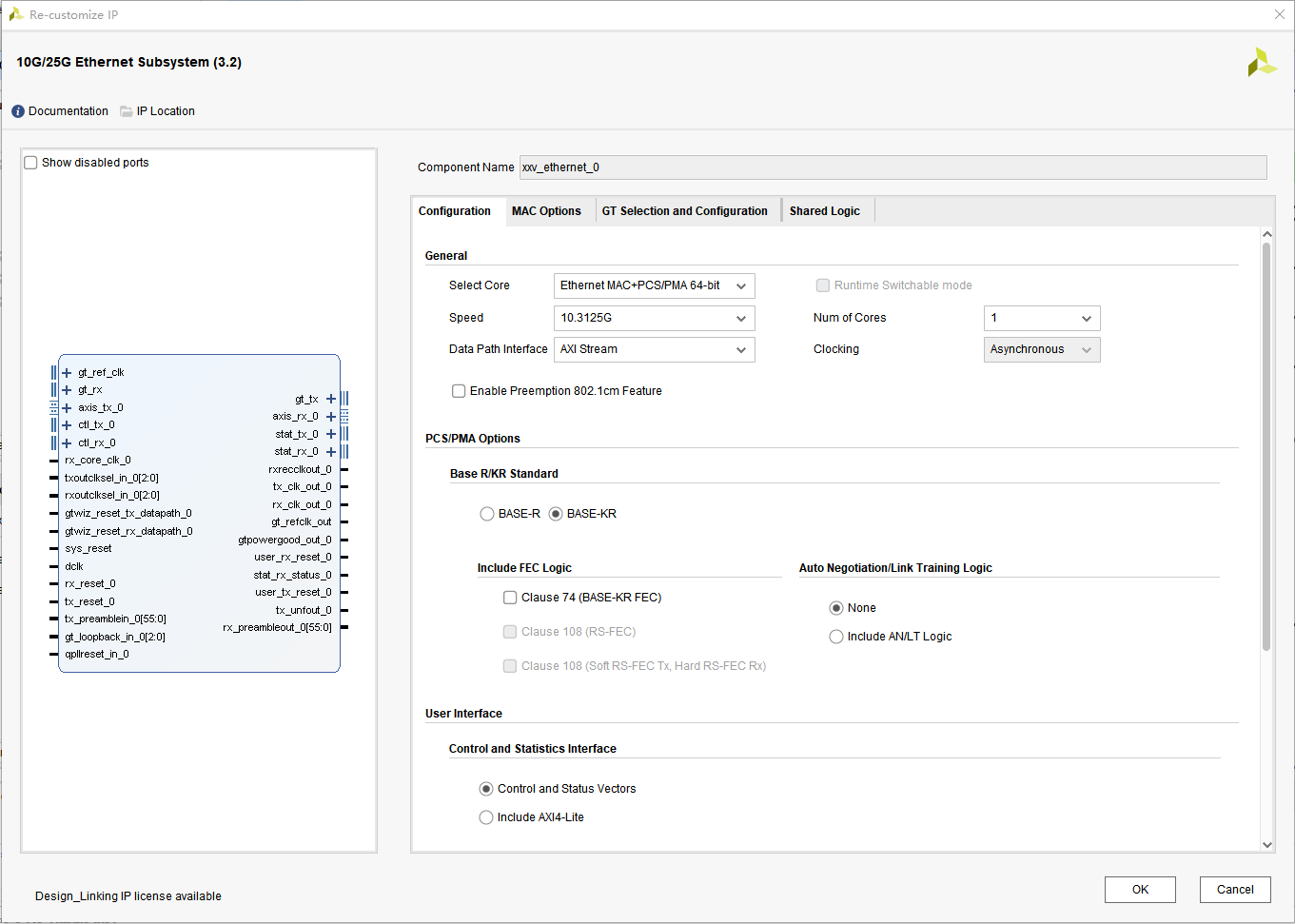

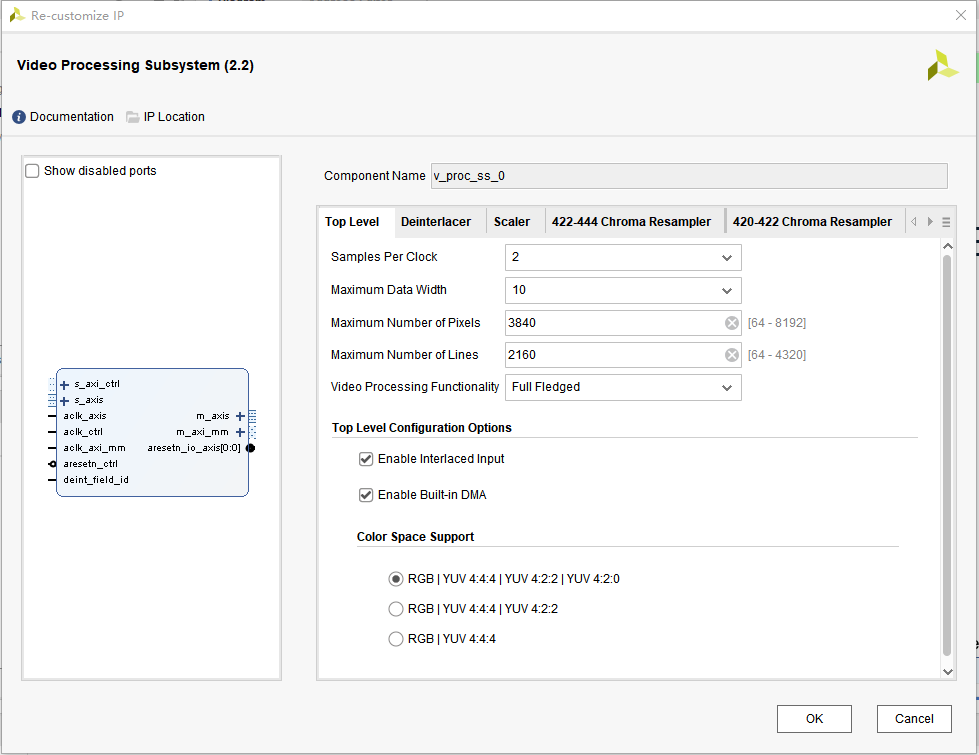

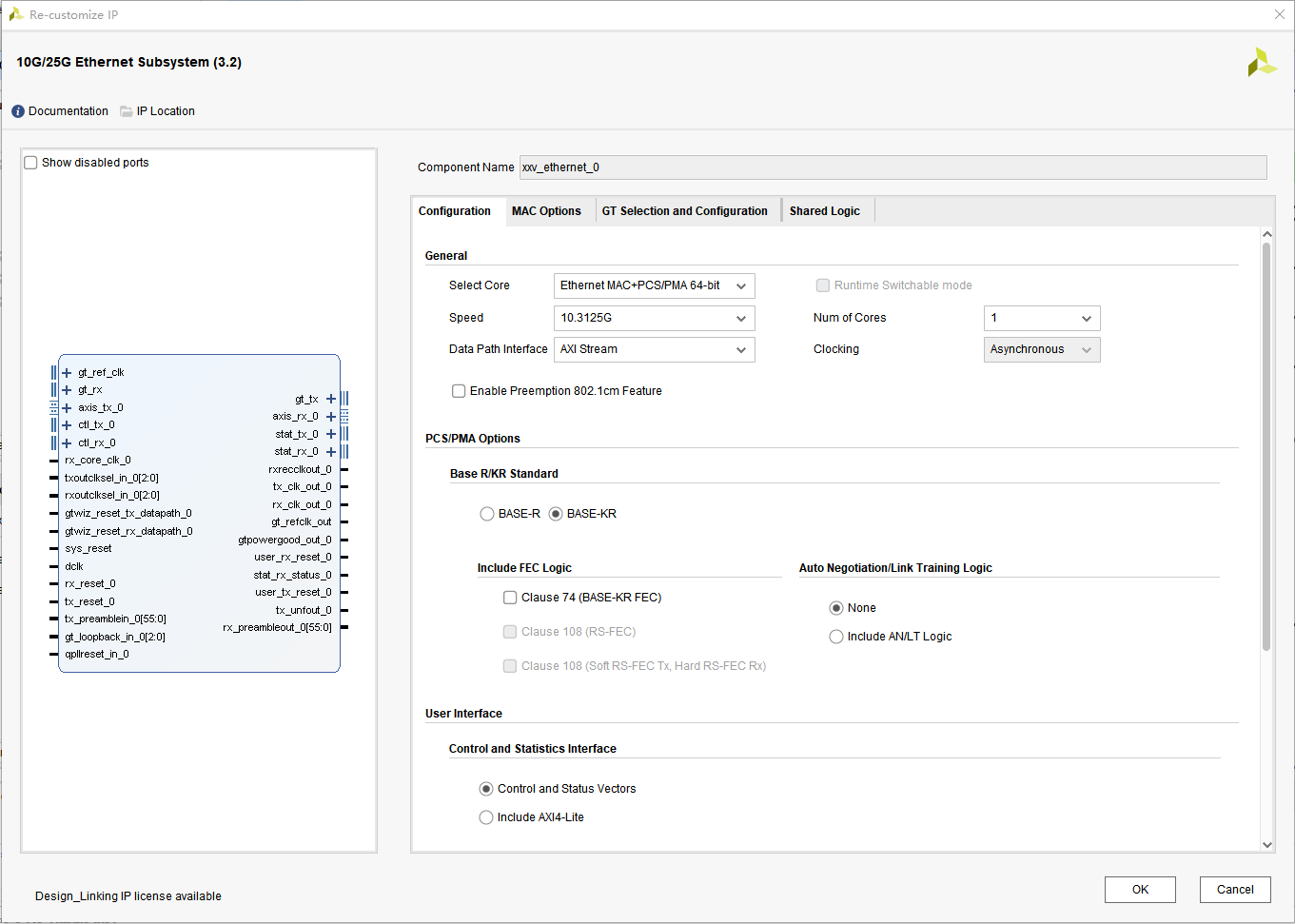

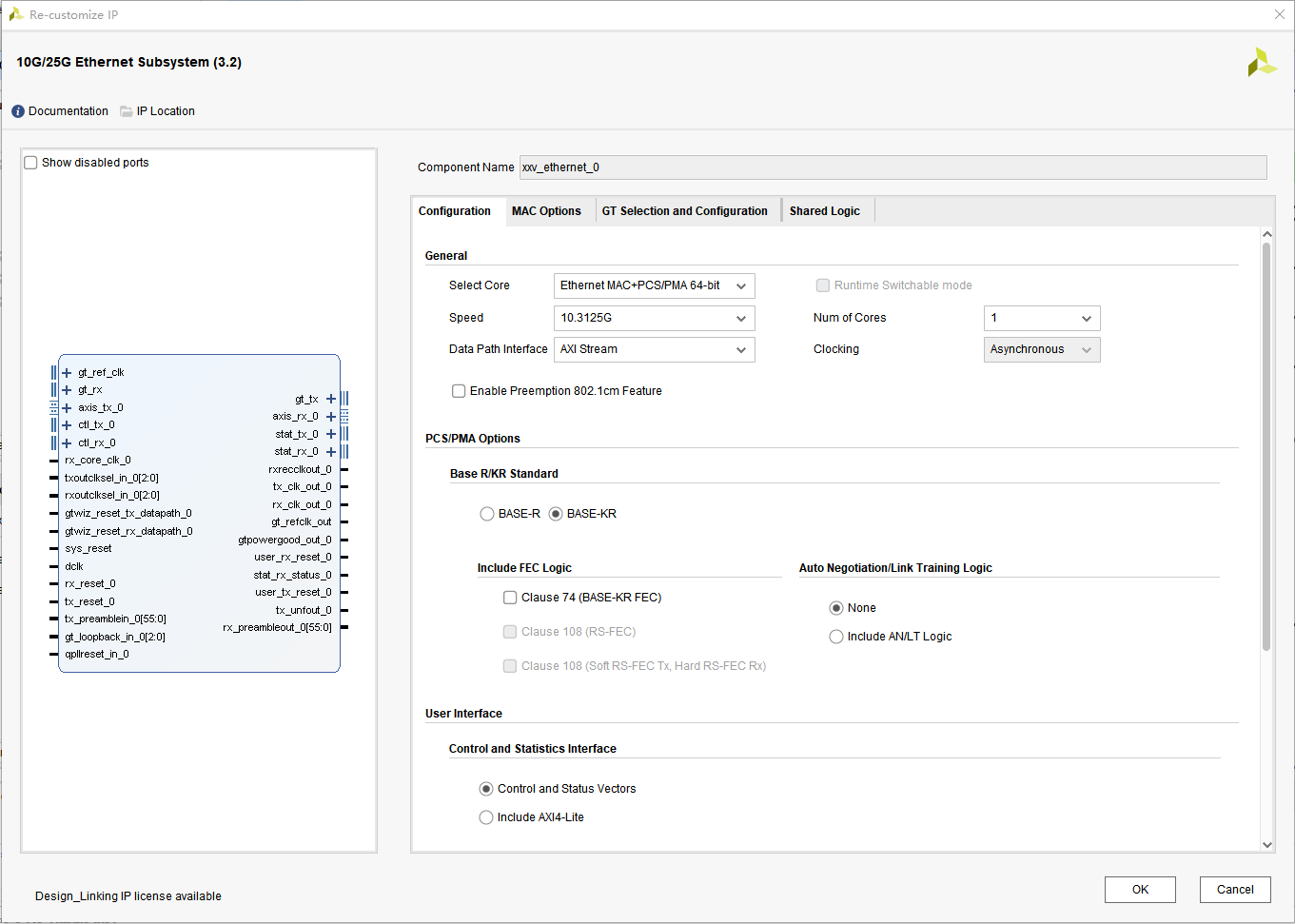

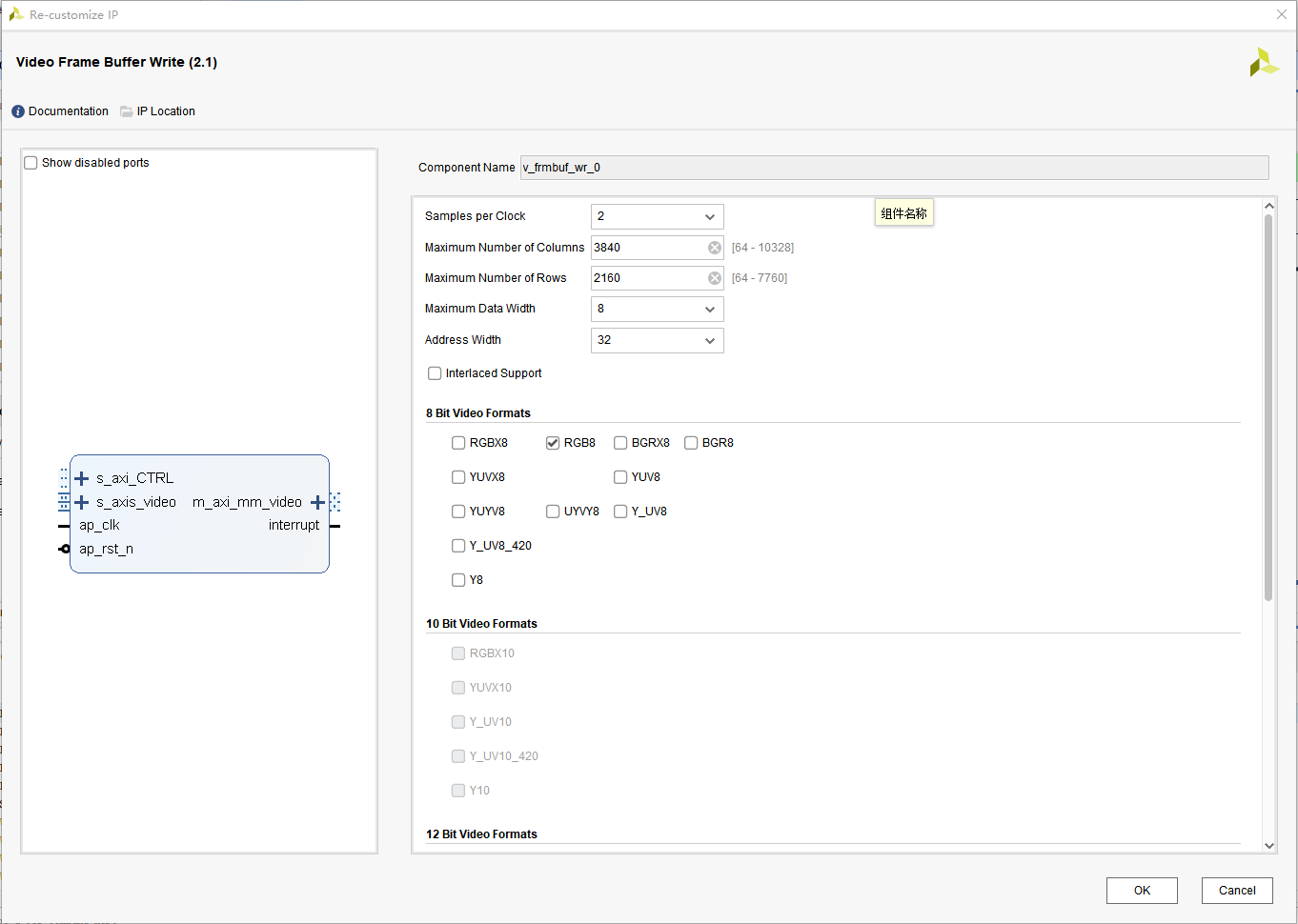

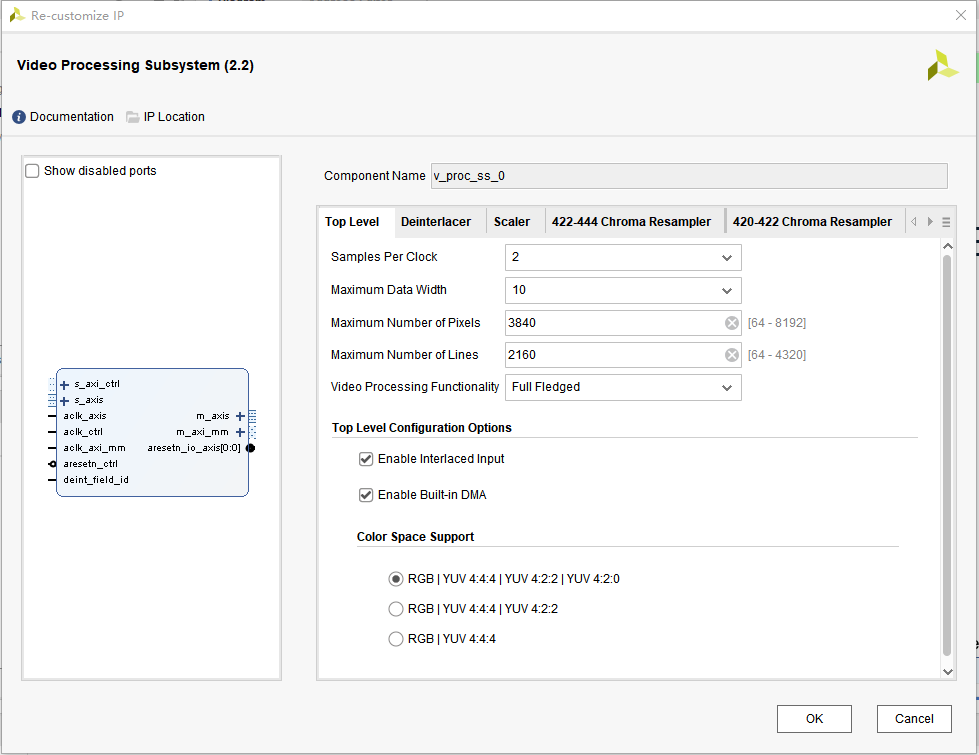

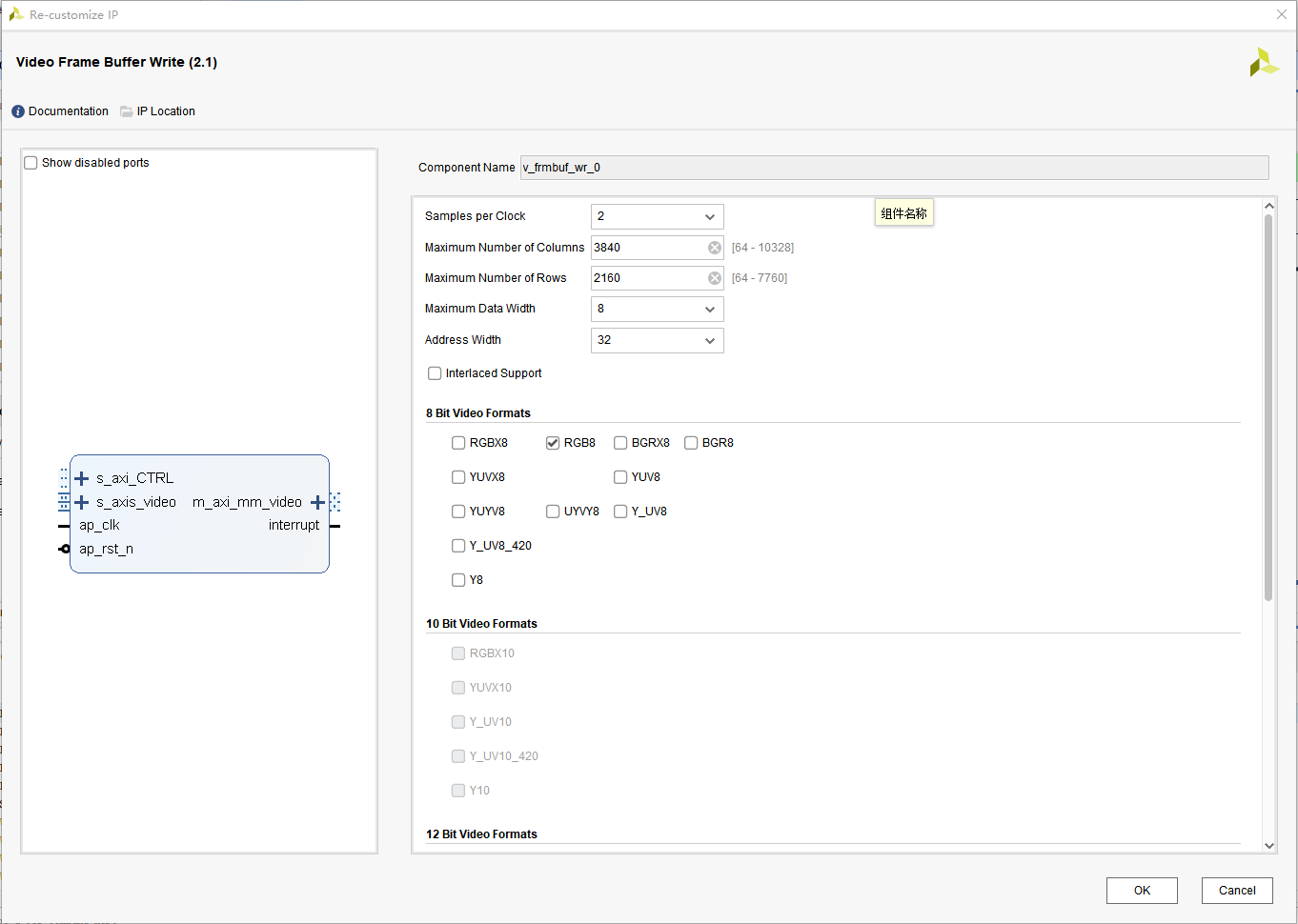

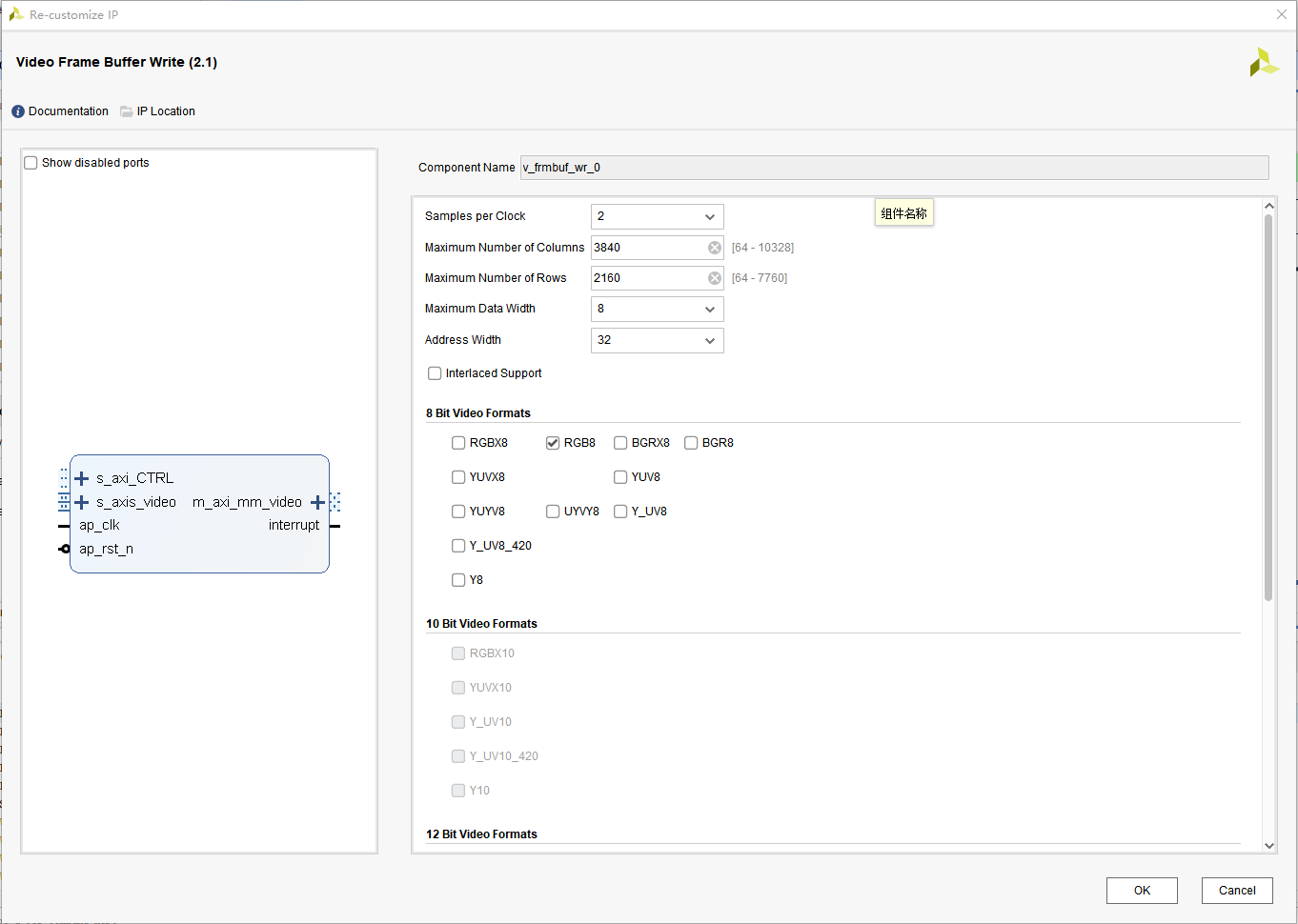

1.视频输入:输入源可以是SDI摄像机、SDI信号发生器或通过HDMI转SDI设备从电脑接入的HDMI信号。视频信号通过TI公司的LMH1219芯片做均衡处理,并将单端信号转换为差分信号后输入FPGA。2.SDI视频解码:FPGA中的UHD-SDI GT IP核用于SDI视频的解串,并将视频信号转换为AXI4-Stream格式供后续处理。通过SMPTE UHD-SDI RX SUBSYSTEM IP核,SDI视频被解码为RGB格式。3.视频帧缓存与处理:解码后的视频信号存储在PS侧的DDR4中,通过Xilinx提供的Video Frame Buffer Write IP核实现。在这一阶段,可以对视频帧进行颜色转换、缩放等处理。4.H.265视频压缩:使用Zynq UltraScale+ VCU IP核对存储的RGB视频帧进行H.265编码压缩。VCU支持YUV420格式的视频,编码分辨率最高可达到4K@60fps。5.SGMII万兆以太网传输:经过H.265压缩后的视频流通过SGMII接口推送至万兆以太网。通过PetaLinux系统,利用TCP/UDP协议将压缩后的码流传输到PC或服务器端,用户可以通过VLC播放器等软件实时播放接收到的H.265码流。

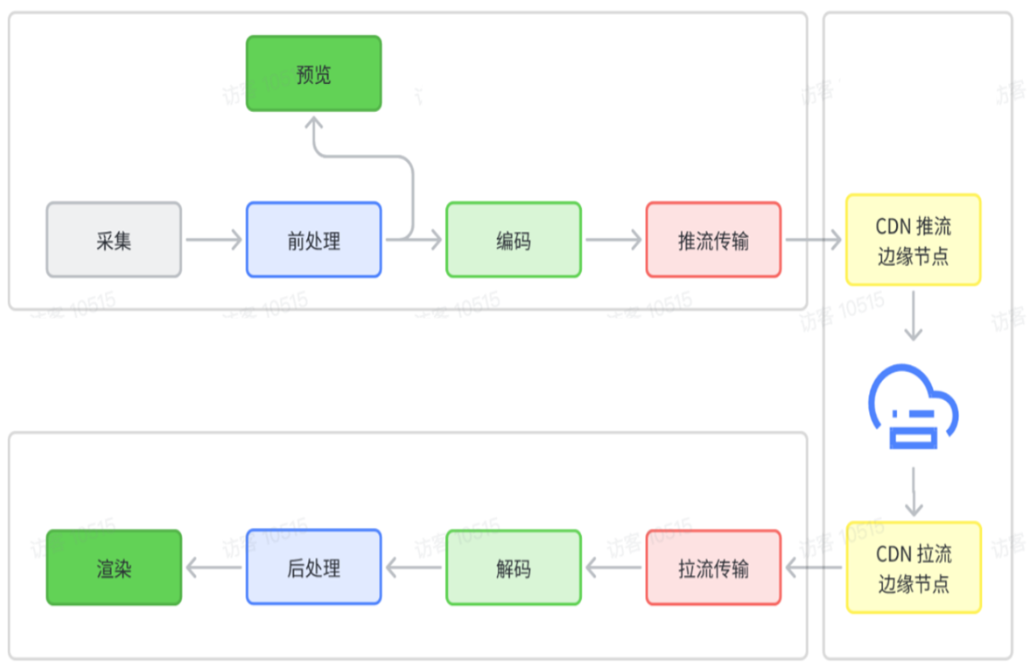

5. 工程设计主要流程

1.SDI输入:通过LMH1219进行信号均衡,SDI信号转换为AXI4-Stream格式。通过HDMI转SDI盒子,通过12G UHD-SDI输出4K 60FPS视频给FPGA,用户也可以使用SDI 工业相机; 2.视频解码:UHD-SDI GT IP核完成视频解串,SMPTE UHD-SDI RX SUBSYSTEM IP核将视频解码为RGB信号。

2.视频解码:UHD-SDI GT IP核完成视频解串,SMPTE UHD-SDI RX SUBSYSTEM IP核将视频解码为RGB信号。

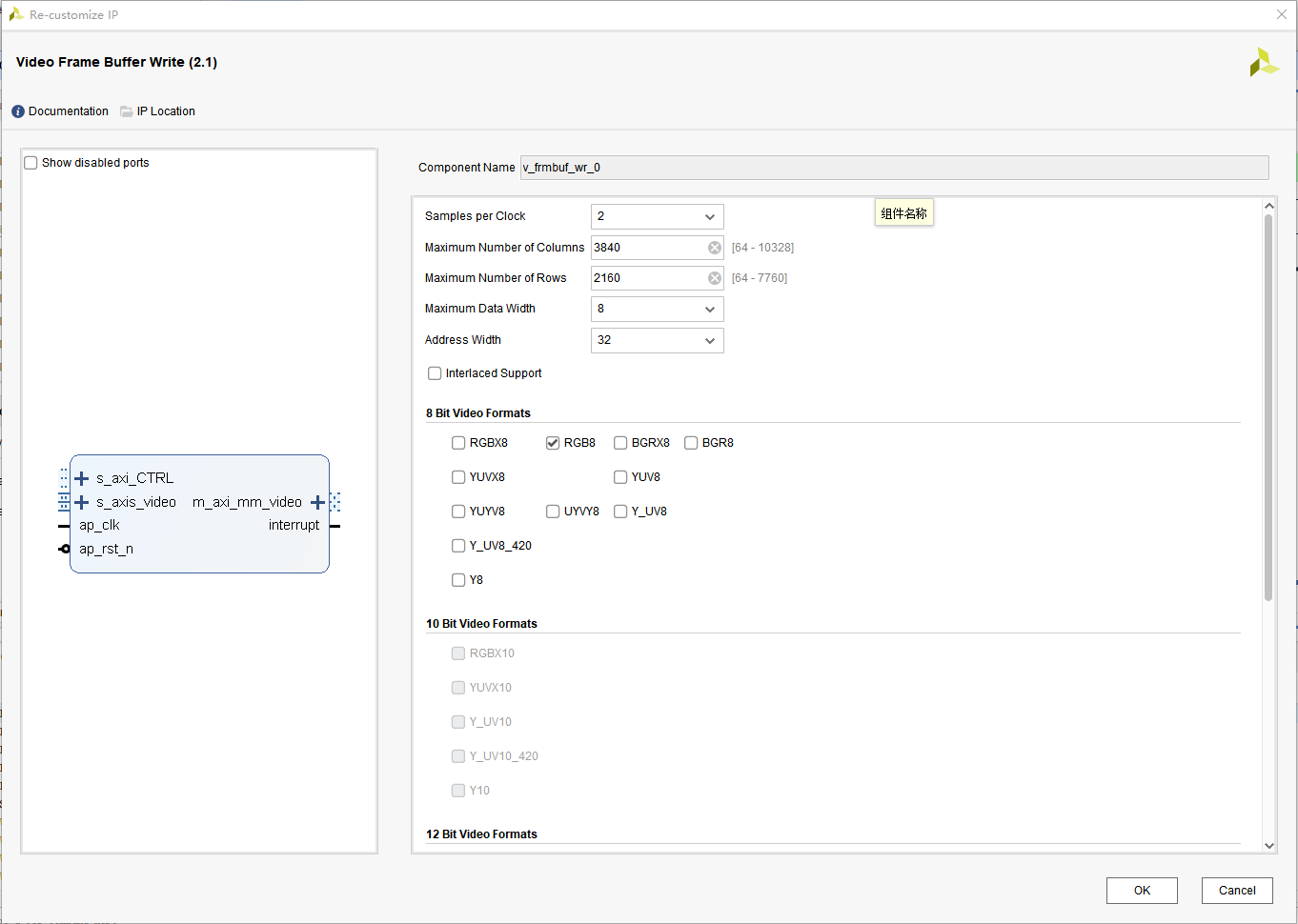

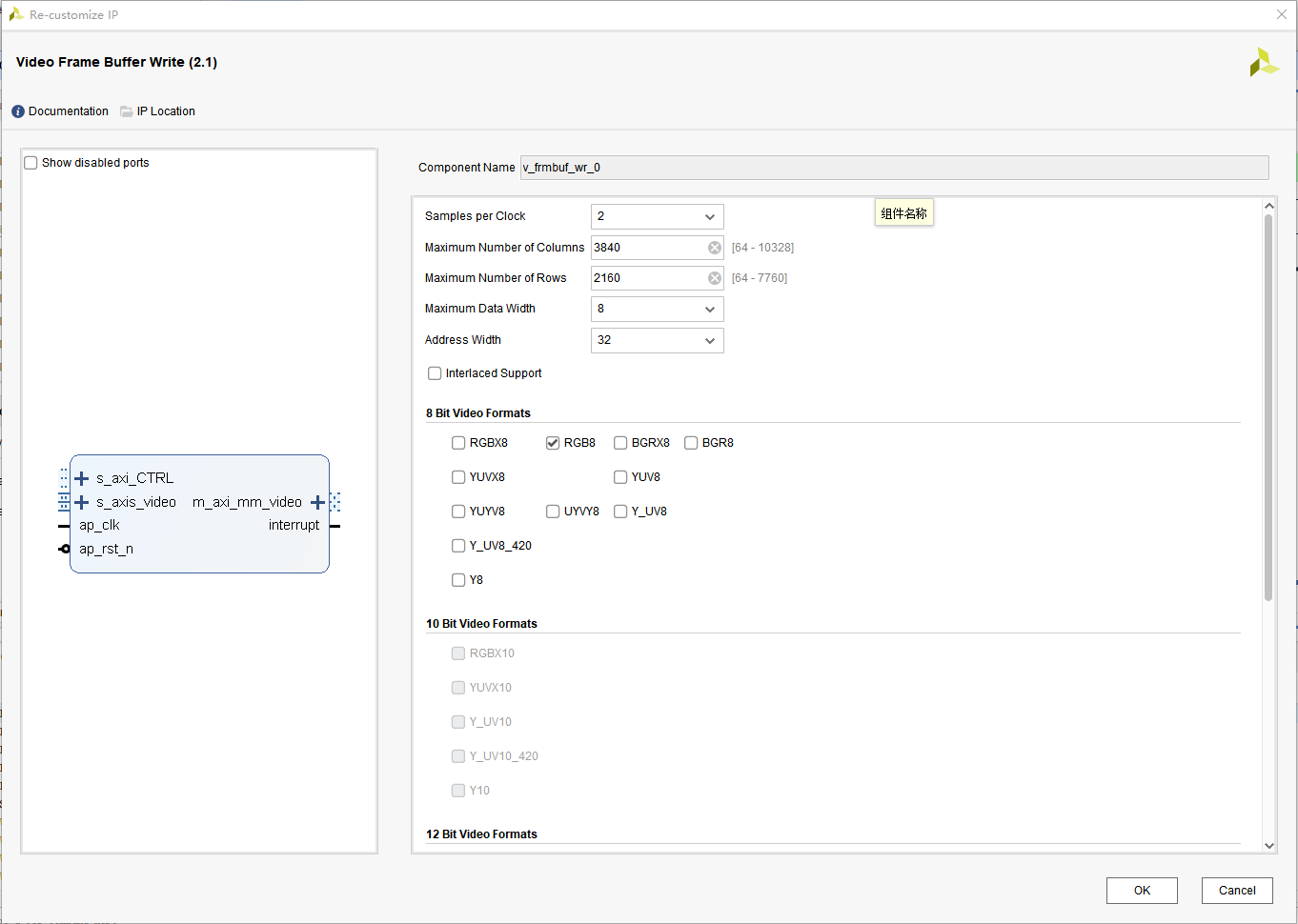

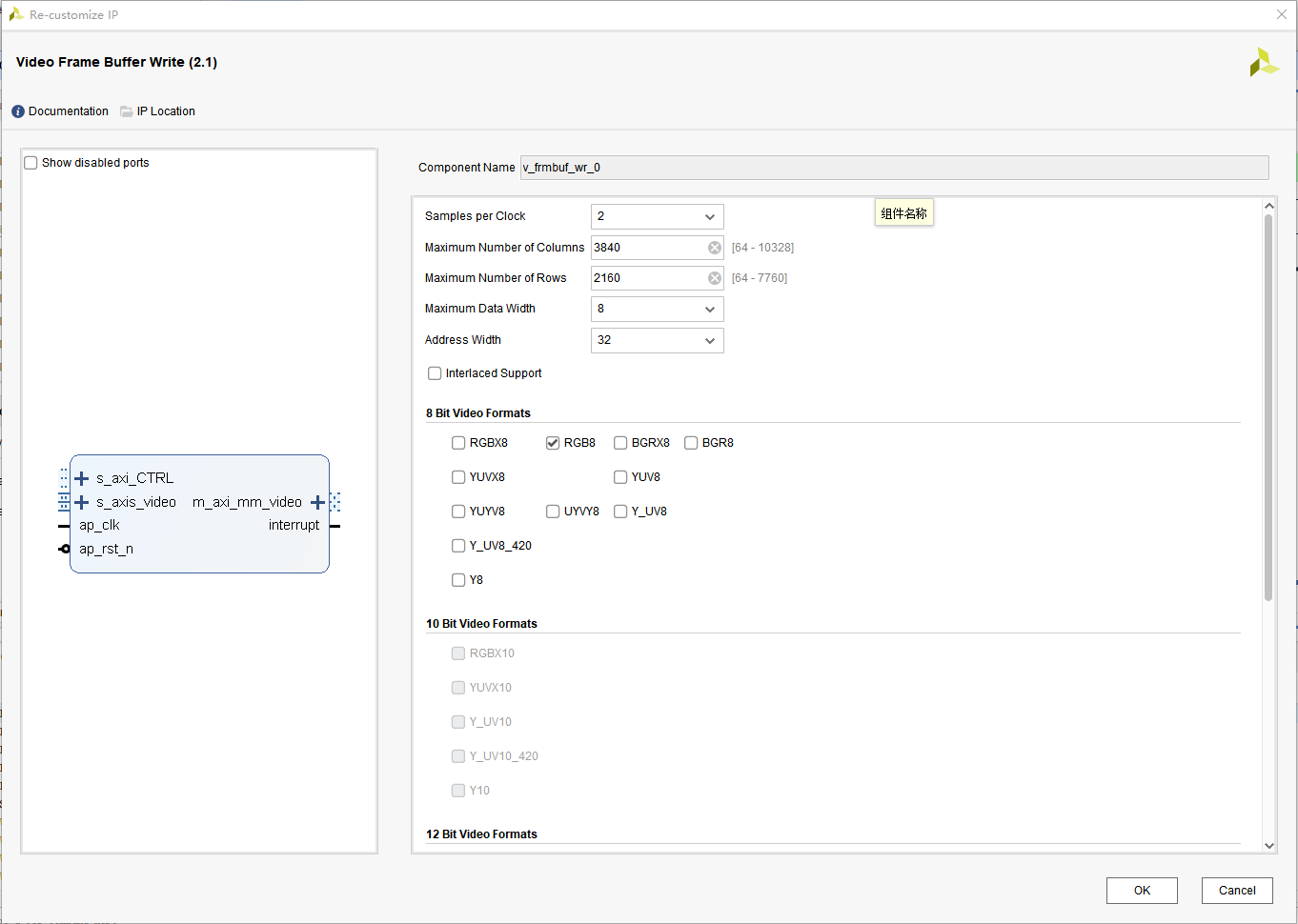

3.视频缓存:使用Video Frame Buffer Write IP核将视频写入DDR4。

用户可以选择在这里做出customer ISP,例如图像缩放,拼接

4.视频压缩:通过Zynq UltraScale+ VCU IP核对视频进行H265压缩。

5.网络传输:通过SGMII万兆以太网接口,将压缩后的H265视频流通过UDP协议推送至PC端,使用VLC播放器播放。

6. 结论

在视频内容不断向4K发展的大背景下, 通过Zynq UltraScale+ MPSoC平台,基于VCU实现的SGMII万兆以太网视频压缩推流方案,不仅能够高效地压缩和传输4K视频,还可以确保较低的延迟和高质量的图像输出。该方案适用于视频监控、医疗影像、工业自动化等对高分辨率视频有需求的应用场景。

对于希望在网络视频平台上获得更好观看体验的用户来说,视频平台和服务提供商则需要在视频编码、网络传输等方面进行优化,以满足用户对于4K视频的画质需求。

7. 互动环节

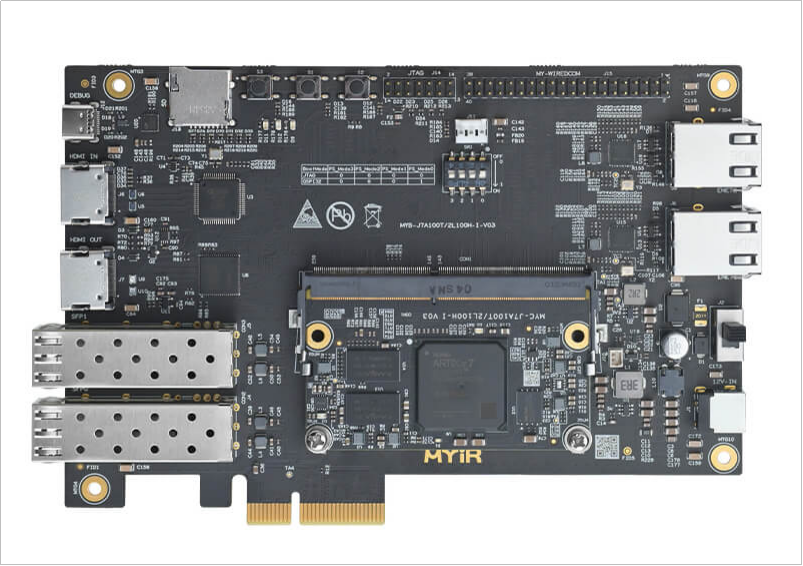

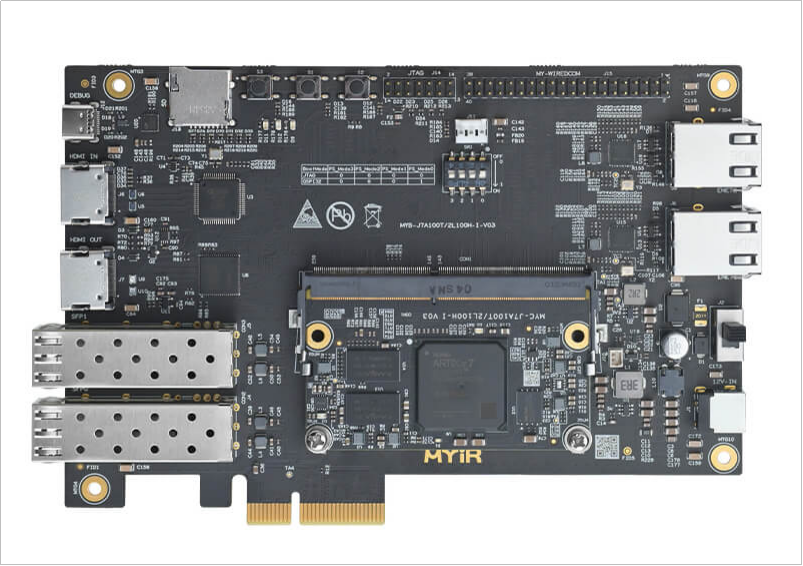

在SGMII网兆以太网推流到PC端,因为是万兆网,CPU无法负担这里的高速吞吐率,这里我们需要用到网络卸载,米尔电子的MYC-J7A100T双芯设计核心板可通过SFP采集SGMII万兆以太网数据后,PC通过PCIE读取视频源,实现万兆网口数据包卸载,我们会在后续系列文章中做出分享基于米尔MYC-J7A100T SFP采集后PCIE XDMA中断读取。

作者: 米尔电子嵌入式, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3881300.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

2.视频解码:UHD-SDI GT IP核完成视频解串,SMPTE UHD-SDI RX SUBSYSTEM IP核将视频解码为RGB信号。

2.视频解码:UHD-SDI GT IP核完成视频解串,SMPTE UHD-SDI RX SUBSYSTEM IP核将视频解码为RGB信号。

/2

/2

文章评论(0条评论)

登录后参与讨论