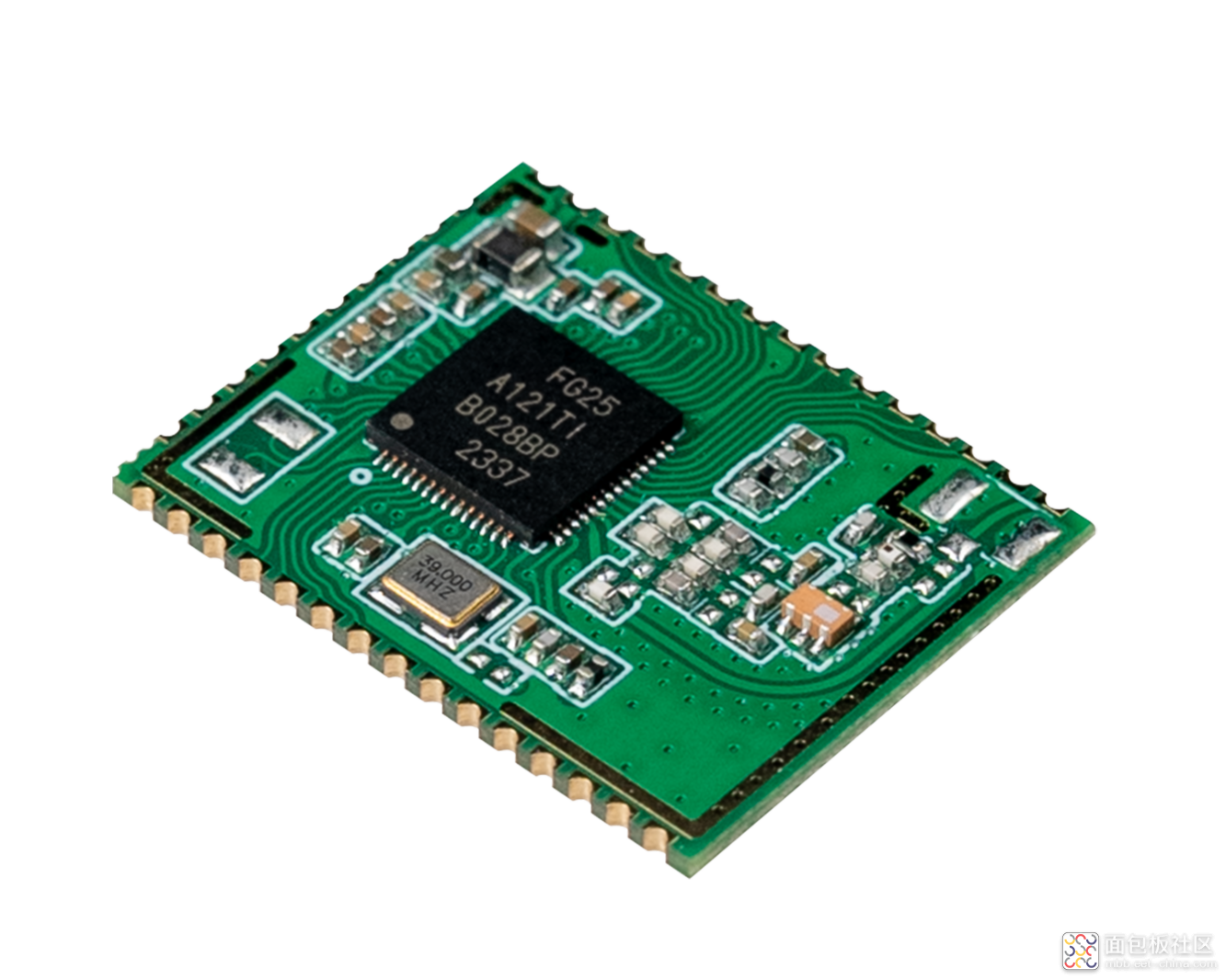

在物联网领域中,无线射频技术作为设备间通信的核心手段,已深度渗透工业自动化、智慧城市及智能家居等多元场景。然而,随着物联网设备接入规模的不断扩大,如何降低运维成本,提升通信数据的传输速度和响应时间,实现更广泛、更稳定的覆盖已成为当前亟待解决的系统性难题。 SoC无线收发模块-RFM25A12 在此背景下,华普微创新推出了一款高性能、远距离与高性价比的Sub-GHz无线SoC收发模块RFM25A12,旨在提升射频性能以满足行业中日益增长与复杂的设备互联需求。值得一提的是,RFM25A12还支持Wi-SUN协议,可为超大规模的户外I/OT网络提供通信基础,降低组网投入,是用于计量、照明和配电自动化的1 GHz以下Wi-SUN的理想解决方案。 RFM25A12 射频收发模块:核心性能大揭秘 RFM25A12工作在470MHz、868MHz与915MHz等多种工作频率下,模块最大射功率为16dBm,接收灵敏度可低至-110dBm,可轻松穿透各种建筑与植被,满足多数物联网场景对于远距离和高稳定性的通信需求。同时,RFM25A12还支持 Wi-SUN MR OFDM MCS 0-6、 802.15.4 SUN MR O-QPSK,带 DSSS、Wi-SUN FSK、 2(G)FSK与 (G)MSK等多种调制方式,能够灵活适配不同的网络架构和应用场景。 RFM25A12 典型应用电路 RFM25A12在EM2深度睡眠模式下,睡眠电流仅为 5uA,功耗极低。RFM25A12的发射电流为65mA @16dBm 915MHz、66mA @16dBm 868MHz、70mA @16dBm 470MHz,接收电流为10mA,可极大地提升物联网设备的电池使用寿命,降低智能表计、传感器等设备的维护频率。 RFM25A12工作在Sub-GHz 频段中,可免受Wi-Fi、蓝牙等2.4GHz频率的干扰,具有天然的抗干扰优势,能准确地传输设备状态信息、控制指令等数据。RFM25A12采用高度集成的模块化设计,极大地简化了系统设计中所需的外围物料,并提供了多个通用I/O,方便用户根据自身需求进行二次开发。 此外,RFM25A12还具备着 1.8V~3.8V的宽电压工作范围,以及-40℃~ 85℃的工作温度范围,并内置了π型匹配电路,简化了天线设计,降低了用户的开发门槛。 精准赋能:多核心场景解决方案 在现代电力系统中, 智能电表作为电力数据采集的关键终端,对于实现电力系统的高效化与智能化管理起着至关重要的作用。为了实现对电力数据的精准采集和高效管理,智能电表的远程抄表和实时数据监控功能需要稳定、可靠的通信技术作为支撑。 RFM25A12 射频收发模块支持多种工业级通信协议,如Wi-SUN、802.15.4等,可确保数据在传输过程中的准确性和完整性,有效避免了数据丢失和误码的情况,且其工作在 Sub-GHz 频段,具有天然的远距离通信能力和抗干扰性能,能够在复杂的环境中实现智能电表与数据采集中心之间的稳定通信。 在街道照明系统中, 构建大规模的物联网路灯网络具有重要意义:一方面可为人们的夜间出行提供安全保障,另一方面能提升城市的形象与品质。为实现对每一盏路灯的精准控制,减少能耗与维护成本,这种大规模的路灯网络需要采用一种低成本、高可靠的组网方案。 RFM25A12 射频收发模块支持多种工业级通信协议,如Wi-SUN、802.15.4等,其采用模块化部署方式,可轻松实现对每一盏路灯的亮度调节。且其还可以根据不同时间节点,天气状况与交通流量,自动调节路灯的亮度,既满足基本照明需求,又能有效降低能耗。 在工业生产过程中, 大量的传感器、执行器等设备需要进行实时的数据交互和远程控制,以实现生产过程的自动化、智能化管理。然而,工业环境复杂多变,对通信技术的可靠性、稳定性和适应性提出了极高的要求。 RFM25A12 射频收发模块支持多种工业级通信协议,如Wi-SUN、802.15.4等,还采用了先进的抗干扰调制技术,能在高温、强电磁干扰等恶劣环境下,准确地传输设备状态数据和控制指令,确保各种工业生产线的高效运行。 展望未来,随着物联网产业的持续发展,它将推动更多传统产业迈向智能化转型,创造出更多高效、节能、便捷的应用场景。而华普微的愿景是通过 RFM25A12 等一系列高性能的射频产品,赋能全球能源、城市、工业的智能化转型,成为客户首选的 “无线连接伙伴”。

标签: SoC

标签: SoC