MCM(Multi-Chip Module):多芯片模块/多芯片组件。多个裸片和其它元器件组装在同一块多层高密度互连基板上进行互连接,然后进行封装,从而形成高密度和高可靠性的微电子组件。它的特征是通过基板电路进行互连,比较可靠,但集成密度低。

相比于技术本身,MCM更多的表现了一种趋势和导向,比如芯片IP化、异构集成、异质集成等,这也是Chiplet的发展方向。Die to Die通过基板电路直接进行互连,比较可靠,成本较低,但集成密度低,延时相对较大。

SiP: SiP(System in Package)是MCM 封装技术进一步发展的产物,是一种密度更高、性能更好的MCM技术。对于某些 IP,无需自己做设计和生产,只需买别人实现好的硅片,然后在一个封装里集成起来,形成一个 SiP。在实现多芯片封装过程中,其目标是在适当扩展面积的基础上,尽可能实现同等功能的 SoC 芯片功能,SiP强调的是系统概念,通过将多种功能的芯片,包括处理器、存储器、FPGA等功能芯片集成在一个封装内,从而实现一个基本完整的系统。粗粗一看,似乎和SoC一样,但区别还是挺大的。

SoC是在同一芯片、同一种工艺下完成的;SiP则可以将不同工艺器件,如MEM、光学器件、射频器件等不同材质、不同工艺节点的设备垂直堆叠或水平排列,做晶圆级别的封装。这是超越摩尔定律的重要实现路径。

SiP的实现需要多种封装技术,如引线键合、倒装芯片、芯片堆叠、基板腔体、基板集成RF器件、埋入式电阻\电容\电感、硅通孔TSV等。

SoC: SoC(system on chip)片上系统。我们台式机的存储器、电源模块、功耗管理模块等都是分开的,而SoC是将这些围绕CPU的关键模块集成在一个芯片上,这样才会有我们的笔记本、手机等小巧强大电子设备。

SoC强调整体设计,包含总线架构、IP核复用、软硬件协同设计、低功耗等技术,将CPU、存储器、各种接口控制模块、互联总线等集成在一起,达到减小面积、提高速度、降低功耗、节约成本等目的。

从不同的 IP 供应商购买一些 IP,软核(代码)或硬核(版图),结合自研的模块,集成为一个 SoC,然后在某个芯片工艺节点上完成芯片设计和生产的完整流程,如下图:

Chiplet: Chiplet即小芯片,相当于将硬核IP再制造成芯片。还是回到SoC,随着工艺节点的推进,成本越来越昂贵,SoC会增大芯片面积,导致良品率下降,成本很高。这时候,AMD给了新方案Chiplet。

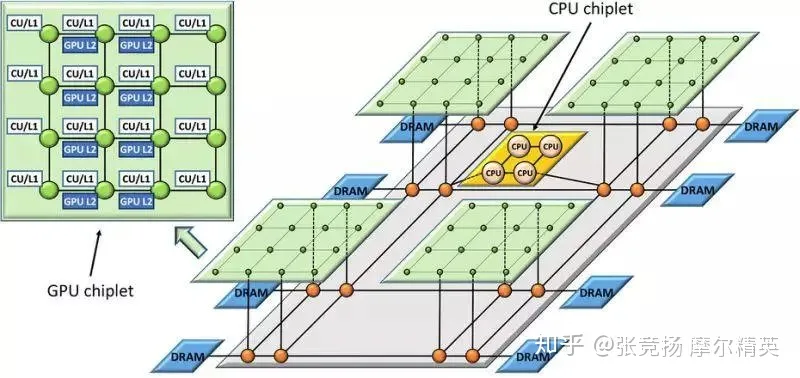

我们可以把Chiplet想象成乐高积木的高科技版本。首先将复杂功能进行分解,然后开发出多种具有单一特定功能,可进行模块化组装的“小芯片”(chiplet),如实现数据存储、计算、信号处理、数据流管理等功能,并以此为基础,建立一个“小芯片”的集成系统。

简单来说,Chiplet技术就是像搭积木一样,把一些预先生产好的实现特定功能的芯片裸片(die)通过先进的集成技术(比如3D integration)集成封装在一起形成一个系统芯片。而这些基本的裸片就是Chiplet。从这个意义上来说,Chiplet就是一个新的IP重用模式。未来,以Chiplet模式集成的芯片会是一个“超级”异构系统,可以带来更多的灵活性和新的机会。

总结:

现在比较普遍的说法是:摩尔定律逐步放缓,半导体行业目前步入后摩尔时代。其实SoC与SiP都是可以让集成电路达到更高性能、更低成本的方式。SoC系统级芯片,是芯片内不同功能的电路高度集成的芯片级产品。SiP既保持了芯核资源和半导体生产工艺的优势,又可以有效突破SoC在整合芯片过程中的限制,克服了SoC中诸如工艺兼容、信号混合、噪声干扰、电磁干扰等困难,大幅降低设计端和制造端成本,同时具备定制化的灵活性。

从芯片设计发展的角度来看,随着电子产品在体积、处理速度或电学特性各方面的需求发展,SoC被确立为未来电子产品设计的关键与发展方向之一。从芯片封装发展的角度来看,由于SoC生产成本过高,技术难度相对较大。SiP能够实现不同源的多个芯片以及不同材质横向及纵向的异质集成,可实现高密度系统级封装,进一步提升产品性能、降低功耗。

随着系统对性能Performance、功耗Power、体积Volume(可简称为PPV,和IC设计中的PPA相对应)的要求越来越高,集成密度的需求也越来越高,SiP也会越来越多地采用先进封装工艺。

简言之:在后摩尔定律时代,IP硬核会逐渐芯片化,形成Chiplet,然后以SiP的形式封装形成系统,使得摩尔定律继续延续下去,这也是摩尔定律的一次革命。

文章来源:https://blog.csdn.net/qq_46675545/article/details/128027666

/3

/3