片上系统或 SoC 是一种集成电路,包含计算机上的大部分组件。顾名思义,它是在硅芯片上制造的整个系统。SoC 的优点在于它将所有组件集成在单个基板上。在半导体中,基板是用于制造集成电路的硅薄膜。与传统主板相比,SoC将可更换组件集成到单个芯片上,从而减小了尺寸并提高了效率。

除了集成电路之外,SoC 还包括软件和用于集成的互连结构。软硬件集成方法使 SoC 的尺寸更小,功耗更低,并且比标准多芯片系统更可靠。

图 1.从 PCB 到 SoC。

SoC 的组件

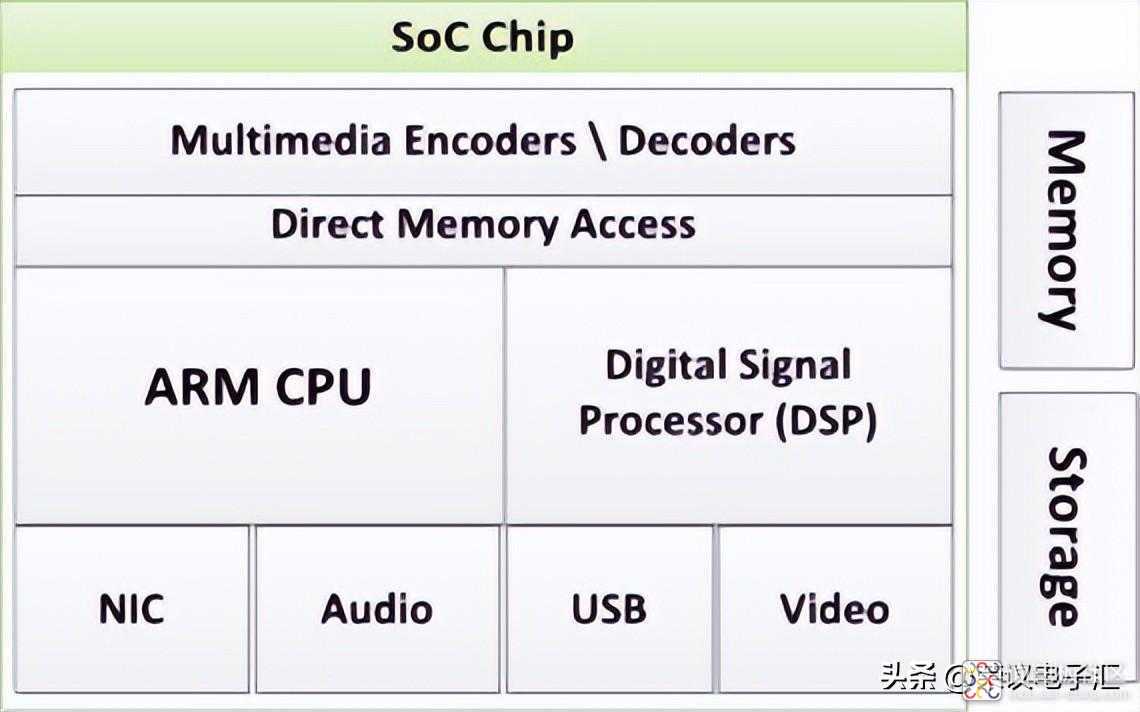

SoC 可分为以下类型:围绕微控制器构建、围绕微处理器构建、针对特定应用构建以及可编程 SoC (PSoC)。SoC 的组成部分包括处理器、主存储器和辅助存储器以及输入/输出端口。其他重要组件包括图形处理器单元 (GPU)、WiFi 模块、数字信号处理器 (DSP) 以及各种外设,例如 USB、以太网、SPI(串行外设接口)、ADC、DAC,甚至 FPGA。通常,它有多个核心。根据各种决定因素和偏好,核心可以是微控制器、微处理器、DSP,甚至 ASIP(专用指令集处理器)。ASIP 具有基于特定应用的指令集。

SoC 可分为以下类型:围绕微控制器构建、围绕微处理器构建、针对特定应用构建以及可编程 SoC (PSoC)。SoC 的组成部分包括处理器、主存储器和辅助存储器以及输入/输出端口。其他重要组件包括图形处理器单元 (GPU)、WiFi 模块、数字信号处理器 (DSP) 以及各种外设,例如 USB、以太网、SPI(串行外设接口)、ADC、DAC,甚至 FPGA。通常,它有多个核心。根据各种决定因素和偏好,核心可以是微控制器、微处理器、DSP,甚至 ASIP(专用指令集处理器)。ASIP 具有基于特定应用的指令集。

通常,SoC使用ARM架构,这是RISC(精简指令集计算)系列,需要较少的数字设计,从而使其兼容嵌入式系统使用。ARM 架构比 8051 等处理器更加节能,因为与使用 CISC 架构的处理器相比,采用 RISC 架构的处理器需要更少的晶体管。这也减少了散热和成本。

下图显示了 SoC 框图的示例。

图 2:SoC 框图示例。

处理器

SoC 的核心是处理器。它通常有多个处理器核心。多个核心允许同时运行不同的进程,这提高了系统的速度,因为它使您的计算机能够同时执行多个操作。基本上,操作系统将多个核心视为多个 CPU,从而提高性能。由于多个内核安装在同一芯片上,因此延迟较短,这是因为内核之间的通信速度更快。多核系统只有一个具有多个核心的 CPU 插槽。例如,以下系统有四个核心和一个插槽。

SoC 的核心是处理器。它通常有多个处理器核心。多个核心允许同时运行不同的进程,这提高了系统的速度,因为它使您的计算机能够同时执行多个操作。基本上,操作系统将多个核心视为多个 CPU,从而提高性能。由于多个内核安装在同一芯片上,因此延迟较短,这是因为内核之间的通信速度更快。多核系统只有一个具有多个核心的 CPU 插槽。例如,以下系统有四个核心和一个插槽。

由于超线程,对于操作系统来说,一个单核表现为两个逻辑单元。超线程允许在两个 CPU 之间共享物理资源。

图 3. 多核处理器示例及其描述。

数字信号处理器 (DSP)

数字信号处理器 (DSP) 是针对数字信号处理操作进行优化的芯片。这包括传感器、执行器、数据处理和数据分析的操作。它可以用于图像解码。使用 DSP 可以节省其他处理任务的 CPU 周期,从而提高性能。专用 DSP 的能效更高,这使得它们适合在 SoC 中使用。DSP 内核使用的指令集是 SIMD(单指令、多数据)和 VLIW(超长指令字)。该架构的使用允许指令的并行处理和超标量执行。DSP 用于执行快速傅立叶变换、卷积、乘法累加等运算。

数字信号处理器 (DSP) 是针对数字信号处理操作进行优化的芯片。这包括传感器、执行器、数据处理和数据分析的操作。它可以用于图像解码。使用 DSP 可以节省其他处理任务的 CPU 周期,从而提高性能。专用 DSP 的能效更高,这使得它们适合在 SoC 中使用。DSP 内核使用的指令集是 SIMD(单指令、多数据)和 VLIW(超长指令字)。该架构的使用允许指令的并行处理和超标量执行。DSP 用于执行快速傅立叶变换、卷积、乘法累加等运算。

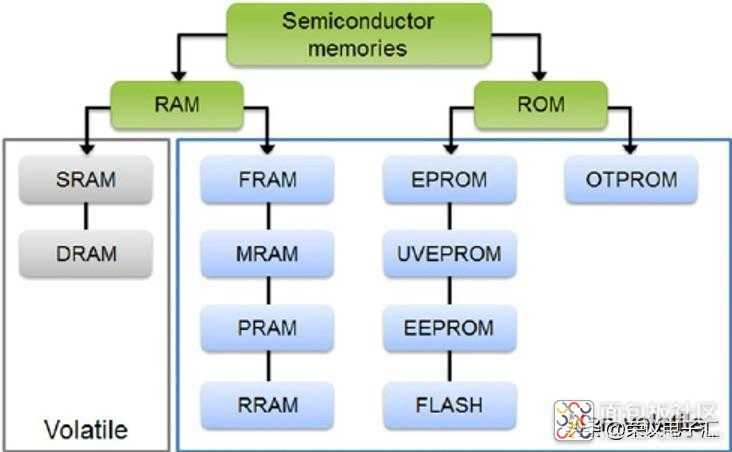

SoC 上的存储器

SoC 具有基于应用程序的存储器。存储器是用于计算目的的半导体存储器块。半导体存储器通常指金属氧化物半导体存储单元,其制造在单个硅芯片上。记忆的类型有:

SoC 具有基于应用程序的存储器。存储器是用于计算目的的半导体存储器块。半导体存储器通常指金属氧化物半导体存储单元,其制造在单个硅芯片上。记忆的类型有:

- 易失性存储器:断电后会丢失数据的存储器。换句话说,他们需要恒定的电源来保留信息。易失性存储器更快、更便宜,这就是它们被频繁选择的原因。

RAM 是一种易失性存储器。最常用的 RAM 是 SRAM(静态 RAM)和 DRAM(动态 RAM)。SRAM 由存储单元组成,存储单元由 1,3 或 6 个晶体管 (MOSFET) 组成。相比之下,DRAM 只有一个 MOSFET 和一个电容器,电容器根据 FET 的状态进行充电和放电。然而,DRAM 很容易出现电容器漏电流。DRAM 的一大优势是它比 SRAM 便宜。如果SoC具有缓存层次结构,则SRAM用于缓存,DRAM用于主存储器。这是因为与主存储器相比,高速缓存需要更快的存储器类型。

还有一些 RAM 类型专为非易失性功能而设计。这些是 FRAM(铁电 RAM)、MRAM(磁阻随机存取存储器),以磁性状态存储数据,PRAM(参数随机存取存储器),在 Macintosh 计算机中用于存储系统设置,包括显示和时区设置。除此之外,还有 RRAM(电阻式随机存取存储器),它有一个称为忆阻器的组件。忆阻器是一种电阻器,其电压根据施加的电压而变化。

- 非易失性存储器:即使在没有电源的情况下也能保留信息的存储器。ROM(只读存储器)是一种非易失性存储器。ROM 的类型包括 EPROM(可擦除可编程只读存储器),它是浮栅晶体管阵列。UVROM(紫外线可擦除可编程只读存储器),使用紫外线擦除并用数据、EEPROM(电可擦除可编程ROM)和闪存重新编程。

所选择的存储器类型取决于设计规范和应用。

图 4:SoC 中半导体存储器的分类。

主要生产半导体存储器的公司有美光科技、英特尔公司、西部数据。

片上通信

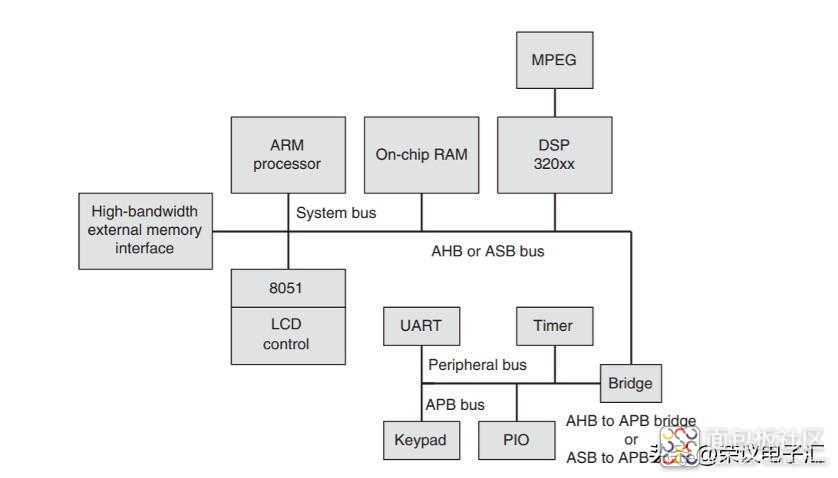

传统上,总线架构用于 SoC 执行单元之间的通信。然而,如今,片上网络互连技术已成为取代总线架构的趋势。

传统上,总线架构用于 SoC 执行单元之间的通信。然而,如今,片上网络互连技术已成为取代总线架构的趋势。

总线通信的一个流行示例是 ARM 的 AMBA(高级微控制器总线架构)总线协议。总线架构用于驱动组件之间的数据。片上总线架构可分为共享总线、分层总线和环形拓扑。不同的公司根据芯片设计和应用设计了不同的架构。例如 Altera AVALON、IBM CORECONNECT、Silicore Corporation 的 WISHBONE。

图 5. SoC 上的 AMBA 总线示例。

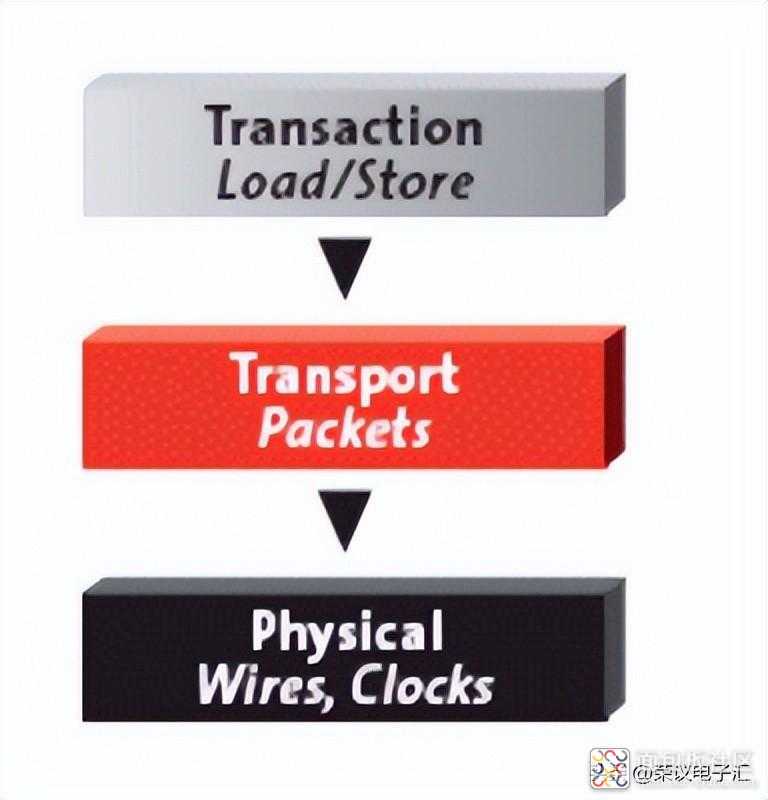

片上网络采用系统级网络技术进行片上流量管理。NOC 是一个同构、可扩展的交换结构网络,用于传输多用途数据包。该架构本质上是通过用户定义的技术分层的。通信通过三层通信方案进行,即事务、传输和物理。

NOC 互连结构的目的是减少片上布线拥塞、更好的时序收敛、一种对 SOC 设计更改各种 IP 的标准化方法。NOC 架构已被证明更加节能并且可以满足吞吐量要求。

图 6. 片上网络的层。

外部接口

SOC 接口根据预期应用而有所不同。外部接口通常基于WiFi、USB、以太网、I2C、SPI、HDMI等通信协议。如果需要,可以添加模拟接口以与传感器和执行器连接。

SOC 接口根据预期应用而有所不同。外部接口通常基于WiFi、USB、以太网、I2C、SPI、HDMI等通信协议。如果需要,可以添加模拟接口以与传感器和执行器连接。

其他组件

功能齐全的 SOC 所需的其他组件包括时钟、定时器、振荡器、锁相环系统、电压调节器和电源管理单元等定时源。

功能齐全的 SOC 所需的其他组件包括时钟、定时器、振荡器、锁相环系统、电压调节器和电源管理单元等定时源。

SoC设计流程

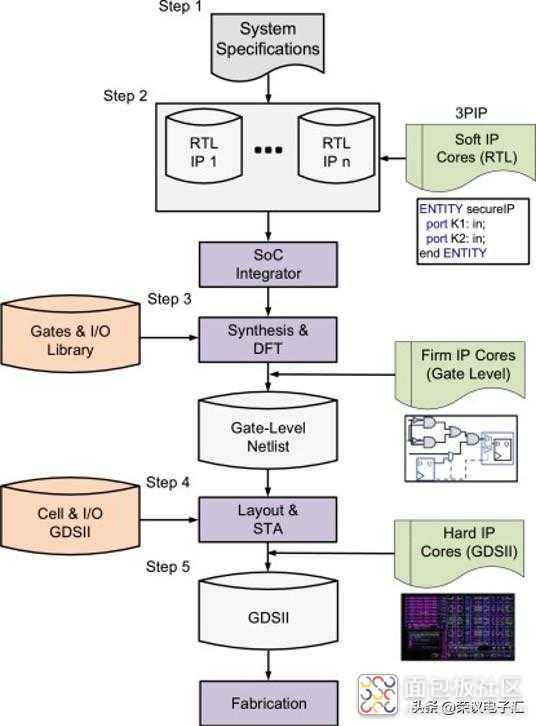

SoC设计流程旨在架构协同设计,即同时设计硬件和软件。设计流程必须考虑优化目标和各种约束。下图是从规格到制造的 SoC 设计流程示例。单独的团队执行制造 SoC 所涉及的每个步骤。

SoC设计流程旨在架构协同设计,即同时设计硬件和软件。设计流程必须考虑优化目标和各种约束。下图是从规格到制造的 SoC 设计流程示例。单独的团队执行制造 SoC 所涉及的每个步骤。

SoC是使用MOS技术制造的。如今,最小的MOS技术是台积电和三星开发的3nm技术。然而,当今大多数设备都使用 10 纳米技术。制造过程涉及设计的网表生成,然后是物理设计流程。在整个过程中,特别关注静态时序分析(STA),即数字电路中的时序计算。STA 还用于验证时序性能并检查任何时序违规。时序违规可能会导致亚稳态,即数字电路中的触发器处于未知状态(既不是 1 也不是 0)。

图 7.SoC 设计流程。

在制造的第 1 步中,分析设计规范,并生成执行规范所需的 IP 列表。这些IP或知识产权通常外包给第三方IP供应商。这些 IP 可以是软核、硬核或硬核,具体取决于更改参数的灵活性级别。IP 也可以由同一家公司制作。

在步骤 2 中,集成 IP 以生成整个设计的 RTL 描述。RTL 代表寄存器传输级,其中包括使用各种硬件描述语言,如 Verilog、System Verilog 和 VHDL。RTL 对硬件寄存器之间的同步数字电路进行建模。

在步骤 3 中,SoC 集成器生成门级网表。门级网表包含有关标准单元逻辑连接的数据,包括组合单元、顺序单元和网络。网络是一组两个或多个互连的组件。可测试设计 (DFT) 工具用于提高可测试性。

在步骤4中,根据物理设计流程将门级网表转换为布局。在此阶段也可以导入IP核。物理设计涉及将设计的电路表示转换为几何形状,从而在制造后产生功能组件。

在步骤 5 中,假设静态时序分析和功耗分析已完成,则开发最终布局并发送进行制造。

在步骤6中,对制作好的芯片进行组装检查。在此步骤之前,要彻底检查芯片的逻辑正确性。这种检查称为功能验证,占该过程的重要部分。为了执行验证,像 SystemC、System Verilog 这样的语言越来越流行以适应复杂性。

重要的是要记住,在制造后对芯片进行任何更改都是非常困难且成本高昂的。因此,设计仿真(原型设计)是在制造之前进行的。这通常使用 FPGA(现场可编程门阵列)来完成,因为它是可重新编程的并且允许调试。

SoC 的优点和缺点

SoC 的主要目标是尽量减少外部组件。因此,与单板计算机相比,它具有以下优点:

SoC 的主要目标是尽量减少外部组件。因此,与单板计算机相比,它具有以下优点:

- 尺寸: SoC 有硬币大小。由于 MOS 技术的尺寸迅速减小,SOC 可以做得非常小,同时能够执行复杂的任务。尺寸不影响芯片的特性。

- 降低功耗: SoC 针对手机等低功耗设备进行了优化。低功耗导致手机电池容量更高。

- 灵活性: SoC 很容易重新编程,这使得它们非常灵活。因此它们允许重复使用 IP。

- 可靠性: SoC 提供高电路安全性并降低设计复杂性。

- 成本效益:主要是由于物理组件较少和设计重用

- 更快的电路操作

SoC 也存在一些缺点:

- 耗时:从设计到制造的整个过程可能需要 6 个月到 1 年的时间。因此,上市需求的时间非常长。

- 设计验证要求非常高,消耗了总时间的70%。由于 SoC 设计的复杂性不断增加,DV 变得乏味。

- IP 的可用性和兼容性起着非常重要的作用,这可以延长上市时间。

- 制造成本呈指数级增加。

- 对于小批量产品,SoC 可能不是最佳选择。

应用

当今 SOC 最常见的应用是移动应用,包括智能手机、智能手表、平板电脑。其他应用包括信号语音处理、PC 接口、数据通信。由于 LTE 和无线网络等通信模块集成到芯片上,SoC 也被应用于个人电脑。

当今 SOC 最常见的应用是移动应用,包括智能手机、智能手表、平板电脑。其他应用包括信号语音处理、PC 接口、数据通信。由于 LTE 和无线网络等通信模块集成到芯片上,SoC 也被应用于个人电脑。

/3

/3