PCI总线定义了两类配置请求,一个是Type00h配置请求,另一个是Type 01h配置请求。

其中HOST主桥或者PCI桥使用Type 00h配置请求,访问与HOST主桥或者PCI桥直接相连的PCI Agent设备或者PCI桥;而使用Type 01h配置请求,需要至少穿越一个PCI桥,访问没有与其直接相连的PCI Agent设备或者PCI桥。在PCI总线中,只有PCI桥能够接收Type 01h配置请求。Type 01h配置请求不能直接发向最终的PCI Agent设备,而只能由PCI桥将其转换为Type 01h继续发向其他PCI桥,或者转换为Type 00h配置请求发向PCI Agent设备。

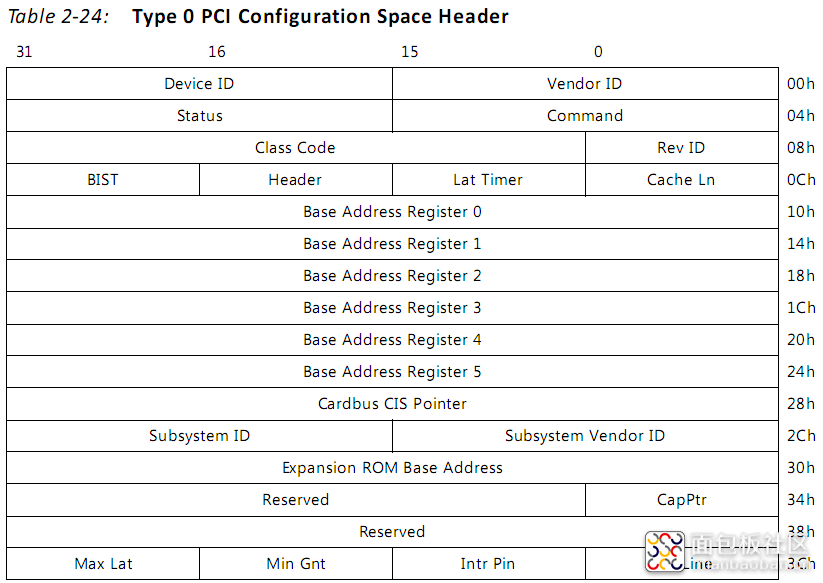

我们在看ursapp_tx代码的时候,发现有很多地方用的Type0配置读和写这两个子程序,后面会给出详细代码。对于配置空间里的基本配置空间需要详细了解。在PG54的45页有详细的说明,下图就是截取于PG054:

注意上图中BAR0到BAR5的地址,分别是从h'10、h'14、h'18、h'1C、h'20、h'24.。下面给出Type0配置读子程序详细代码,注意代码中trn_td的位宽是128bit,在64bit模式中,需要两次赋值,每次64bit,总共128bit。

为了更好地理解上述代码,我们还需要了解一个概念,即TLP(Transaction Layer Packet)。当处理器或者其他PCIe设备访问PCIe设备时,所传送的数据报文首先通过事务层被封装为一个或者多个TLP,之后才能通过PCIe总线的各个层次发送出去。

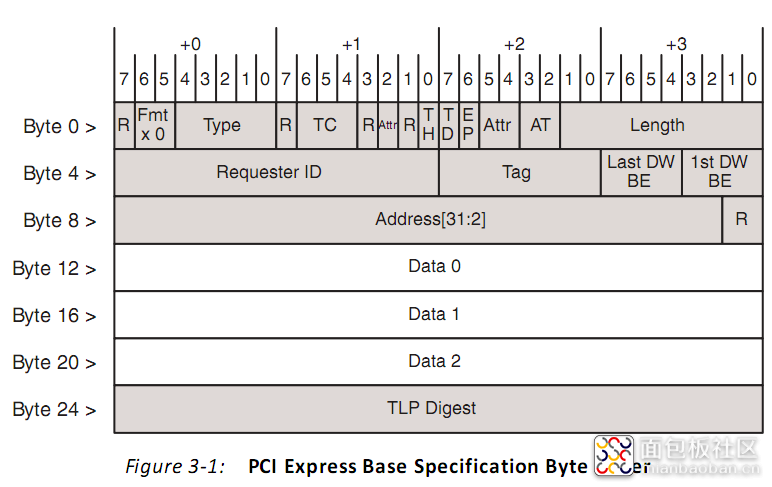

一个完整的TLP由1个或者多个TLP Prefix(由协议引入,FPGA开发可以不关注)、TLP头、Data Payload(数据有效负载)和TLP Digest组成。TLP头是TLP最重要的标志,不同的TLP其头的定义并不相同。TLP头包含了当前TLP的总线事务类型、路由信息等一系列信息。在一个TLP中,Data Payload的长度可变,最小为0,最大为1024DW。

TLPDigest是一个可选项, 一个TLP是否需要TLP Digest由TLP头决定。DataPayload也是一个可选项,有些TLP并不需要DataPayload,如存储器读请求、配置和I/O写完成TLP并不需要Data Payload。

TLP头由3个或者4个双字(DW)组成。其中第一个双字中保存通用TLP头,其他字段与通用TLP头的Type字段相关。一个通用TLP头由Fmt、Type、TC、Length等字段组成,如下图(截取PG054第46页,这是典型32位地址存储器写请求TLP格式)所示。需要注意的是,上述代码的格式和下图的不太一样,除了第一个DW外,其它2个或3个DW都与具体的Type类型有关。

如果存储器读写TLP支持64位地址模式时,TLP头的长度为4DW,否则为3DW。而完成报文的TLP头不含有地址信息,使用的TLP头长度为3DW。

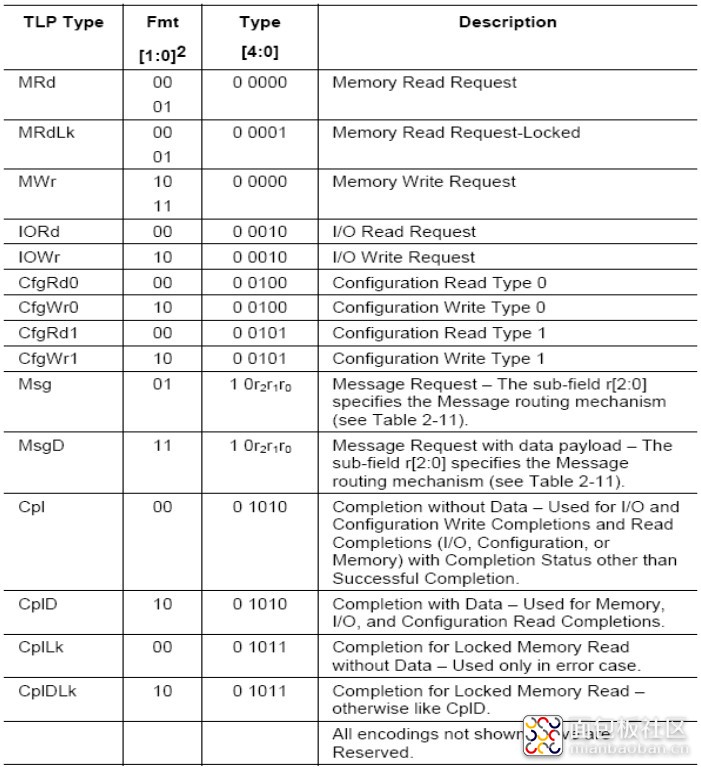

FMT=“00” 表示TLP大小为3个双字,不带数据。

“01” 表示TLP大小为4个双字,不带数据。

“10” 表示TLP大小为3个双字,带数据。

“11” 表示TLP大小为4个双字,带数据。

FMT和Type详细解码如下:

下面介绍Length字段的意义,如此对应TLP基本就有个大概认识了:

在存储器读请求TLP中并不包含Data Payload,在该报文中,Length字段表示需要从目标设备数据区域读取的数据长度;而在存储器写TLP中,Length字段表示当前报文的DataPayload长度。Length字段的最小单位为DW。当该字段为n时,表示需要获得的数据长度或者当前报文的数据长度为n个DW,其中0代表0x3FF。值得注意的是,当n等于0时,表示数据长度为1024个DW。

上述代码中Length字段是1,读取某个BAR空间状态信息,将返回一个DW的信息。在TSK_BAR_SCAN子函数里,使用Type0配置读,扫描各个BAR并将扫描得到的信息存储在全局变量中,以备后续使用。

关于PCIe的基础知识,这里有篇文章,介绍的非常好:https://blog.csdn.net/cllovexyh/article/details/79828833

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/1

/1

文章评论(0条评论)

登录后参与讨论