看了一篇《神奇的硬件秒速边沿检测技术》的blog,看了一遍没看懂,于是自己也模拟了一下,看波形图,看着看着突然一下子开窍了,哈哈,实践出真知!

我的边沿检测模块edge_detect程序如下:

module edge_detect(

CLK,RSTn,

SIG_detected,

H2L_flag

);

//最开头是模块外部输入输出信号和数据

input CLK; //50MHz主时钟

input RSTn; //低电平复位信号,

input SIG_detected; //被测信号

output H2L_flag; //1->0标志信号

//内部寄存器和接线

reg H2L_flag1;

reg H2L_flag2;

reg H2L_flag3;

//reg H2L_flag4;

always @ (posedge CLK or negedge RSTn)

if(!RSTn) begin

H2L_flag1<=1'b1;

H2L_flag2<=1'b1;

H2L_flag3<=1'b1;

// H2L_flag4<=1'b0;

end

else begin

H2L_flag1<=SIG_detected;

H2L_flag2<=H2L_flag1;

H2L_flag3<=H2L_flag2;

// H2L_flag4<=H2L_flag3;

end

assign H2L_flag=H2L_flag3&(~H2L_flag1); //negative脉冲边沿检测

endmodule

生成的RTL视图如下:

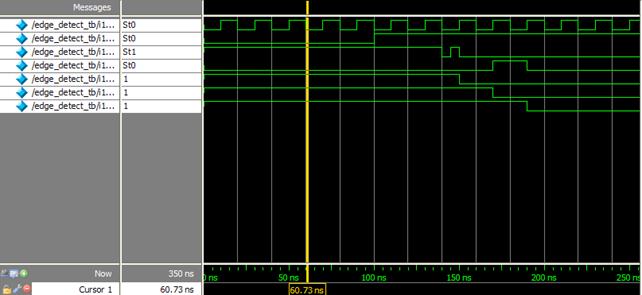

仿真波形如下:

为什么几个触发器搭起来就能进行边沿检测呢?道理现在看看真TMD简单:每一个dff就延迟一拍时钟,虽然延迟了,但从dff的Q端输出的信号仍然是最初的输入信号电平状态(只是比输入端口延迟了而已,也就是把输入端初始状态经过几个时钟周期保存下来),而取反相与的是输入信号现在的电平状态(没有经过延迟),也就是说如果一个输入信号最初是状态1,几个时间段后输入信号变成状态0,即同一个信号从1跳变到0,傻子都知道这个信号是发生了下降沿跳变。 注意这里只是边沿检测不是延时消抖!!!!!

当前输入信号求反再和延迟后的同一个输入信号相与,目的是为了产生一个时钟周期的高电平作为跳变的标志位,而且想延迟多少时间就加几个dff。

/2

/2

用户377235 2012-8-24 16:38

程序编译不能通过,assign 语句等号左边不能为reg类型,而必须为wire类型,不知道你的结果是怎么出来的?

用户1634340 2011-8-27 13:34