这段时间工作比较忙,USB就放了几天.今天又再开动.

今天的任务是复位电路.

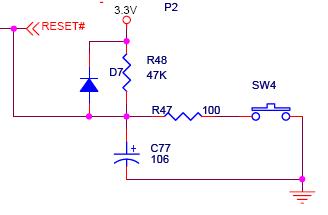

复位电路的作用在系统中有多重要大家心理都应该很清楚了吧.但FPGA的复位电路一般都是由一个电容一个电阻一个二级管外加一个按键开关组成的简单的复位电路.如下图:

这个电路在系统接电后由3.3V经过R47给C77充电,此时RESET上得到低电平.经过一段时间后,C77被充满,RESET点电平升高.最后稳定在高电平.这是接电后的情况,即上电复位.

另一个情况是当按下SW4时,C77经过R47放电到地,RESET被瞬间拉到低电平,当按键放开后,C77再次通过R48充电,经过一段时间后稳定到高电平.完成手动复位.

但光是这个复位电路对于我们来说是不够的.由于FPGA是高速电路,在按键复位开关按键的时候会产生抖动,生成很多毛刺方波,这对于我们的电路来说是很有害的.所以有必要设计一个可靠的复位电路.电路要求如下:

可靠复位,按下复位键后,复位输出0,延时200mS后,输出1,此期间不管复位按钮的状态.

主要的想法是这样的:

用一个计数器计数主时钟每200mS定时检测复位输入线的状态,当发现输入产生下降沿时,输出复位低电平,同时用另一个计数器开始计数主时钟.延时200ms后,复位输出高电平.此时复位完成.

https://static.assets-stash.eet-china.com/album/old-resources/2009/7/30/e3d18677-de2a-432e-9c23-e2002f3a606c.rar

/1

/1

文章评论(0条评论)

登录后参与讨论