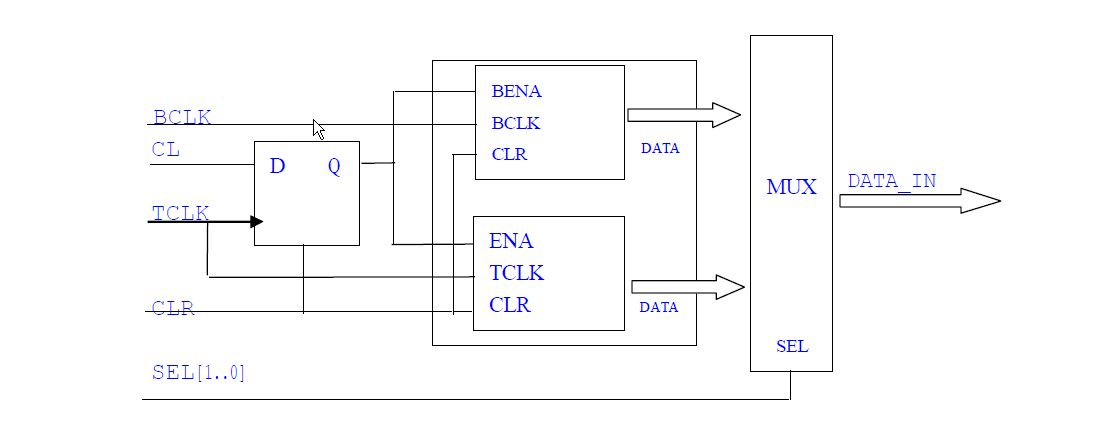

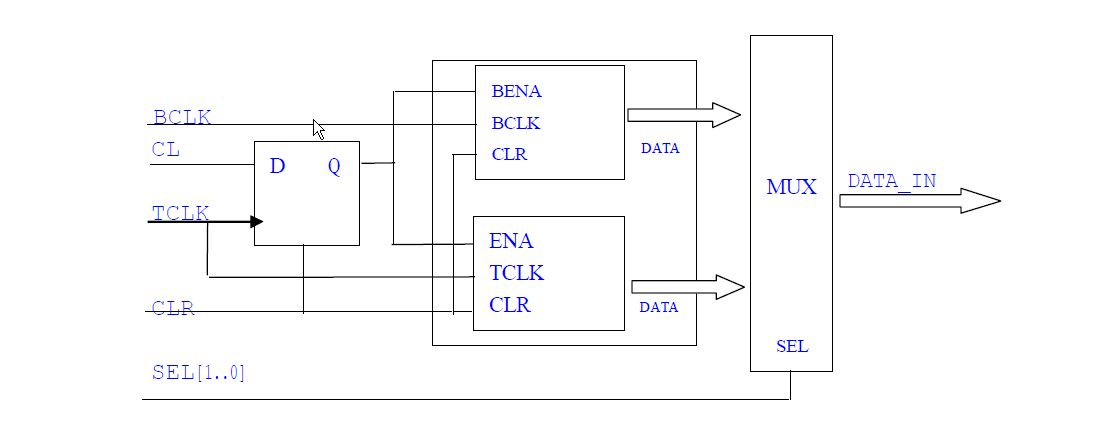

等精度测量的原理:

其实很简单,就是你找一个基准,这个基准和信号在一个控制信号的控制下同时开始同时结束,然后比较一下就得到的。使用FPGA做,由于其并行可以做起来其实很简单,但是。。。我遇到的问题不这里,而是后面的通讯问题

等精度的FPGA:

module fre_cnt(clk_std,clk_sig,rst_n,Gate_n,cnt_std,cnt_sig,Gate_t);

input clk_std;

input clk_sig;

input rst_n;

input Gate_n;

output Gate_t;

output [31:0]cnt_std;

output [31:0]cnt_sig;

reg [31:0]cnt_std;

reg [31:0]cnt_sig;

///////////////////////

reg Gate_t;

//将门控信号和输入信号的上升沿同步

always @ (posedge clk_sig or negedge rst_n)

begin

if(!rst_n)

Gate_t <= 1'b0;

else

Gate_t <= Gate_n;

end

//对clk_sig计数器计数

always @ (posedge clk_sig or negedge rst_n)

begin

if(!rst_n)

cnt_sig <= 32'h00000000;

else if(Gate_t)

begin

cnt_sig <= cnt_sig + 32'h00000001;

end

end

//对 clk_std计数

always @ (posedge clk_std or negedge rst_n)

begin

if(!rst_n)

begin

cnt_std <= 32'h00000000;

end

else if(Gate_t)

begin

cnt_std <= cnt_std + 32'h00000001;

end

end

endmodule

其实大家都在说

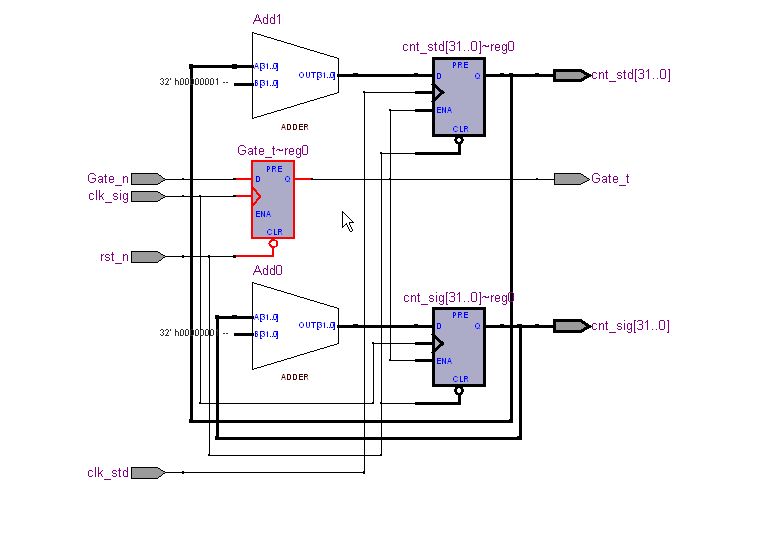

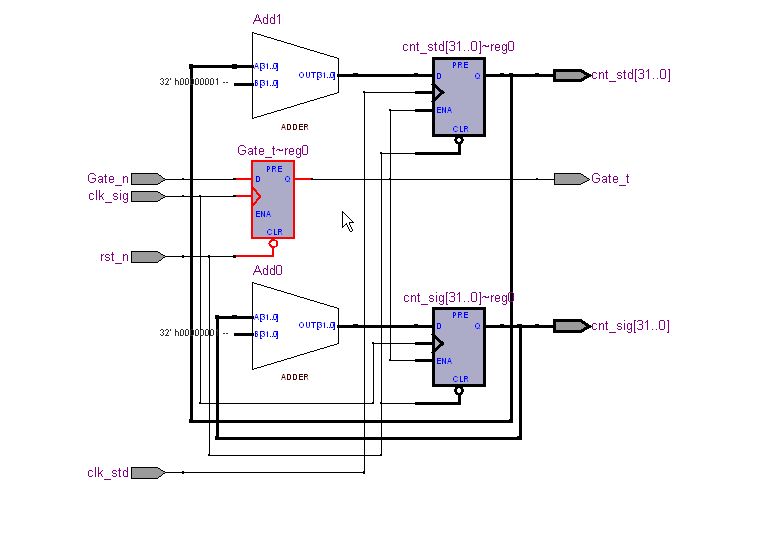

其实综合以后的RTL是:

不是计数器而是累加器

测量的结果在12HZ以上的精度可以做到10^-5,频率小于12hz的时候,信号计数器会在1个单位跳jieg变,得到的结果和实际说的早整个范围内的精度不变有差异,是本身结构的问题还是我们同步的处理上出现的问题。。。。进行中

7-20号问题补充:

问题在于我知道后面有个同步周期,在gate信号结束后需要等待信号的下周期上升沿,但是这个信号我没有相似FPGA里面做结束信号,而是使用的单片机的延时,在频率低的时候这个延时的时间不能够满足延时的需要所以出现不稳定的情况。。。。

问题并没有解决,cnt_sig计数器在整个量程范围内都有一个偶尔的跳变,并且随着频率的增加跳变的概率就增大,虽然最精度的影响还可以接受,只在最后几位跳变,但是不应该出现这种情况 还有一个问题需要补充,gate信号最好增加一个同步信号

always@(posedge clk_std)

begin

Gate1 <= Gate_n;

end

always@(posedge clk_std)

begin

Gate2 <= Gate1;

end

always@(posedge clk_std)

begin

Gate3 <= Gate2;

end

//将门控信号和输入信号的上升沿同步

always @ (posedge clk_sig or negedge rst_n)

begin

if(!rst_n)

Gate_t <= 1'b0;

else

Gate_t <= Gate3;

end

这样控制信号就会避免受到毛刺的干扰

/5

/5

tengjingshu_112148725 2009-7-20 14:30