N_odd_divider.v / Verilog

module N_odd_divider (

input i_clk,

input rst_n,

output o_clk

);

parameter N = N_odd; // 设置奇数(除1外)倍分频

parameter M = ?; // M="N/2"

// bit_of_N: N_odd的二进制位宽

reg [(bit_of_N - 1):0] cnt_p; // 上升沿计数单位

reg [(bit_of_N - 1):0] cnt_n; // 下降沿计数单位

reg clk_p; // 上升沿时钟

reg clk_n; // 下降沿时钟

assign o_clk = clk_n & clk_p; // 按位与(作用:掩码)

// 上升沿计数器: 0~(N-1)

always @ (posedge i_clk or negedge rst_n)

begin

if (!rst_n)

cnt_p <= 0;

else

begin

if (cnt_p == N-1)

cnt_p <= 0;

else

cnt_p <= cnt_p + 1'b1;

end

end

// 生成上升沿时钟

// 0~(N>>1) ↑ -> 1; ((N/2)+1)~(N-1) ↑ -> 0

always @ (posedge i_clk or negedge rst_n)

begin

if (!rst_n)

clk_p <= 0;

else

begin

if (cnt_p <= M) // 0 ~ (N/2)

clk_p <= 1;

else

clk_p <= 0;

end

end

// 下降沿计数器: 0~(N-1)

always @ (negedge i_clk or negedge rst_n)

begin

if (!rst_n)

cnt_n <= 0;

else

begin

if (cnt_n == N-1)

cnt_n <= 0;

else

cnt_n <= cnt_n + 1'b1;

end

end

// 生成下降沿时钟

// 0~(N>>1) ↓ -> 1; ((N/2)+1)~(N-1) ↓ -> 0

always @ (negedge i_clk or negedge rst_n)

begin

if (!rst_n)

clk_n <= 0;

else

begin

if (cnt_n <= M) // 0 ~ (N/2)

clk_n <= 1;

else

clk_n <= 0;

end

end

endmodule

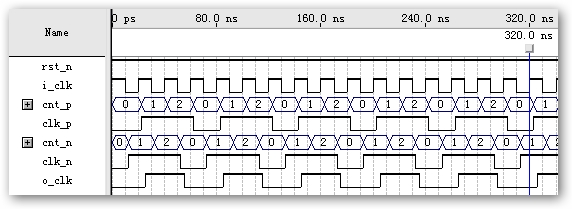

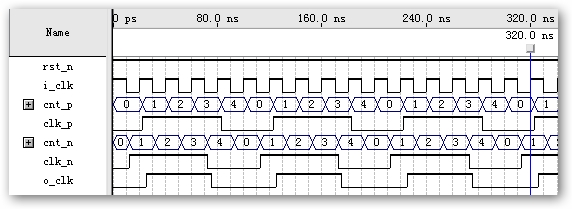

仿真波形

图1. N_odd = 3

图2. N_odd = 5

另见

/5

/5

用户171203 2008-10-8 17:55