格雷码: 任意两个相邻的代码之间, 只有一位二进制数不同的BCD码. 常用在大于24个状态的状态机设计中.

一. 自然二进制码转换为二进制格雷码

原理: 若二进制码表示为: B[N-1]B[N-2]...B[2]B[1]B[0];

相应地, 则二进制格雷码表示为: G[N-1]G[N-2]...G[2]G[1]G[0].

其中最高位保留: G[N-1] = B[N-1];

其他各位: G = B[i+1] xor B. (i = 0, 1, 2, ..., n-2)

Binary_to_Gray.v / Verilog

module Binary_to_Gray (

input [N-1:0] B,

output reg [N-1:0] G

);

parameter N = N_bit_Binary; // 设置自然二进制码的位宽

integer i;

always @ (B)

begin

G[N-1] = B[N-1];

for (i=0; i<N-1; i="i"+1)

G = B[i+1] ^ B;

end

endmodule

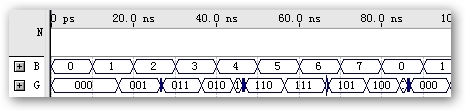

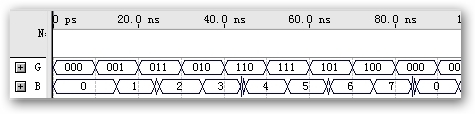

仿真波形

图1. N="3"图2. N="4"

二. 二进制格雷码转换为自然二进制码

原理: 若二进制格雷码表示为: G[N-1]G[N-2]...G[2]G[1]G[0];

相应地, 则二进制码表示为: B[N-1]B[N-2]...B[2]B[1]B[0].

其中最高位保留: B[N-1] = G[N-1];

其他各位: B[i-1] = G[i-1] xor B. (i = 1, 2, ..., n-1)

Gray_to_Binary.v / Verilog

module Gray_to_Binary (

input [N-1:0] G,

output reg [N-1:0] B

);

parameter N = B_bit_Gray; // 设置二进制格雷码的位宽

integer i;

always @ (G)

begin

B[N-1] = G[N-1];

for (i=1; i<=N-1; i="i"+1)

B[i-1] = G[i-1] ^ B;

end

endmodule

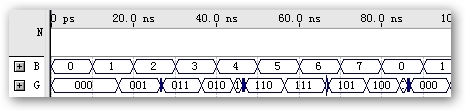

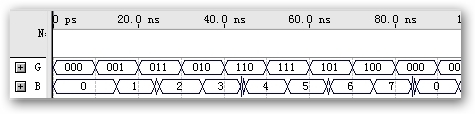

仿真波形

图3. N="3"

图4. N="4"

三. 故障分析

在转换时, 出现很多毛刺, 不知怎样消除. 希望有高人指点.

四. 其他

本文可作为Verilog的for循环的学习实例.

五. 参考资料

/4

/4

用户1455274 2009-8-7 13:53