使用HDL Designer 加速设计之流程配置

HDL Designer Series是Mentor公司一款针对FPGA和ASIC工程中“设计创建”和“流程管理”的工具。HDL Designer Series为提高设计效率和设计质量提供了灵活手段和功能。通过图形化、文本或两者的组合,结合IP的引入,快速高效的创建设计,HDL可视 化和统一的HDL风格和文档能力,版本管理为团队设计提供了基础,全面的VHDL、Verilog和mixed-HDL支持适应百万门的FPGA, ASIC和SoC设计。与仿真工具如ModelSim/NC-Verilog和综合工具如DC/Synplify/Precision结合提供完整的FPGA/ASIC设计流程。

HDL Designer Series的功能涵盖设计输入与管理程序所有层面:HDL Pilot?提供设计管理;HDL Detective?提供设计分析与文件记录;HDL Author?提供文字与图形编辑以及文件记录;HDL Designer?把单点工具所有功能和更强大文件记录能力结合成单一解决方案;Debug Detective则把除错和设计分析能力提供给ModelSim仿真解决方案。HDL Designer Series同时提供硬件描述语言设计、分析与管理功能,是电子设计自动化产业最完整的工具套件;此外,HDL Designer Series还支持所有常用的仿真与合成工具。

2,流程配置

HDL Designer Series秉承的理念是“任意供应商”、“任意流程”、“任意输入”,也就说要提供一个统一的管理平台。HDL Designer Series之所以能够在各个流程之间自由切换,全是因为现在各个EDA软件都支持后台脚本语言,比如TCK/TK等,如果你是个“脚本达人”,自己写好脚本,同样可以在后台调用各个软件。

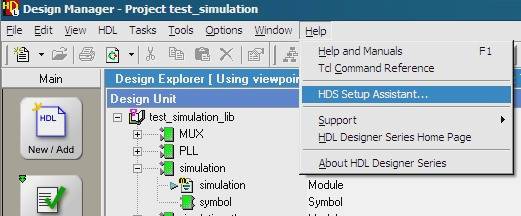

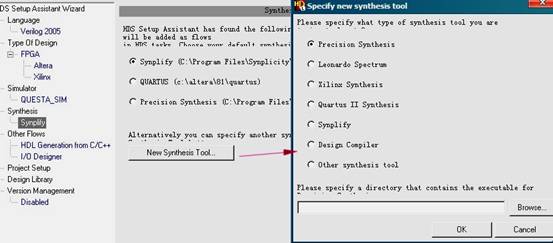

软件安装完之后,会自动让你进入流程设置,如果你想更改或者重新设计,则先点击软件Help—>HDS Setup,如下图所示。

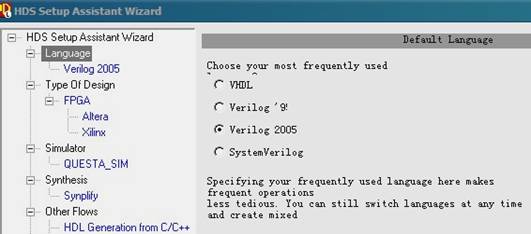

进入设置以后,首先需要选择“编程语言”,如Verilog,System Verilog或者VHDL等,当然软件本身还支持“真值表”、“状态机”、“ASM”等方法输入,只是在此不用设置。

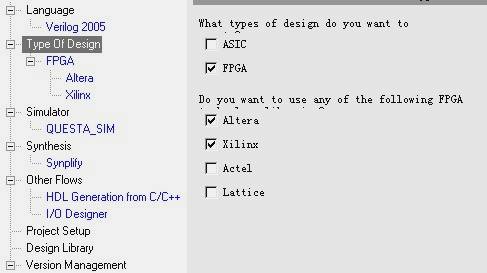

接下来是设置设计类型,是ASIC还是FPGA,如果是FPGA的话,又是哪一家供应商,ALTERA还是XILINX等,这样以便于系统调用相应指令。

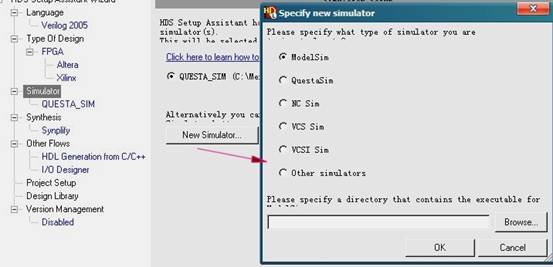

再继续就是设置仿真器,HDL Designer Series支持当前所有流行的仿真器,如NC-Verilog,VCS,Modelsim等。目前主流的几大仿真器各有优缺点,差异不是很大,一般做IC设计,选用NC-Verilog或VCS,做FPGA设计则Modelsim/Questasim/Active-HDL。当然你也可以自己选择其他的仿真软件,只要设置相应的路径即可。

再下一步就是综合器的设置了。同样,HDL Designer Series也支持当前主流的几大综合器。现在各个综合器的之间的性能差距已经不是非常大了,做Altera设计一般情况下Quartus自带的综合器即可,如果要使用第三方的,Synplify和Perecision都是蛮好的选择;XILINX的话一般推荐使用Synplify和Perecision;从事数字ASIC设计当然是DC了,Cadence的ENCOUNTER也有不错的口碑,不过Synopsys才是这个市场的老大,也别是把Synplicity收购了之后,Mentor和Cadence的日子越加不好过了。

最后就是设置一些系统级的东西,如C/C++的代码转换和板级设计的IO designer,在此不在赘述。

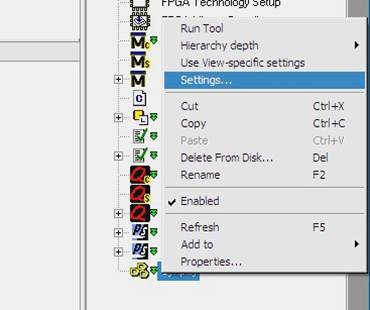

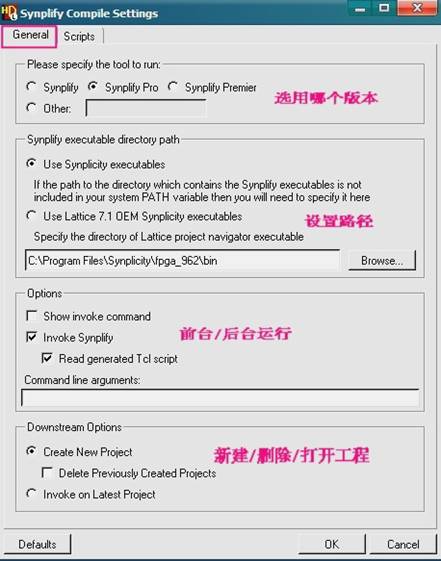

系统设置完成以后,在软件右侧既可以看到各个流程所对应的logo。有一些软件如Synplify,有Synplify,Synplify Pro,Synplify Premier等多个版本,那么如何设置,才能让HDL Designer Series调用自己想使用的版本呢?

对应logo右击,进入Setting,既可以看到针对各个版本的设置信息和脚本信息。同样的,如Precision也有Precision RTL Plus、Precision RTL和Precision Physical等版本,同样是可以按此设置。

流程设置好了之后,在软件主界面的Option下还可以设置“语言模板”、“头文件”等等其他信息,在此不做一一讨论,大家自己去摸索吧。

/4

/4

文章评论(0条评论)

登录后参与讨论