Xilinx DDR控制器使用中的一些问题

XILINX 公司在最新的Spartan6中集成了MCB硬核,它可以支持到DDR3-800,而且对于大多数厂家的存储芯片都支持(Micron、Elpida、Hynix.....)。对于工程来讲,其MCB硬核优秀的误码校验和偏移时钟校验,以及PLL_ADV工作时的稳定、高精度都大大保证了研发产品的质量。而对于用户控制接口又是以通用FIFO的读写方式,代替复杂的DDR/DDR2/DDR3读写逻辑。以SRAM的地址映射方式代替复杂的行列地址选择。可见spartan6—MCB硬核控制器的诞生是值得大家推崇的。

一, 在工程中添加IP

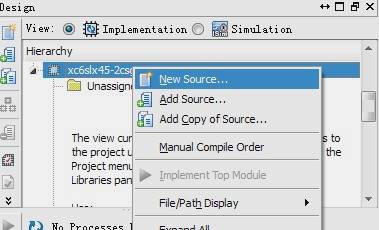

1、 打开工程,添加新的源文件,

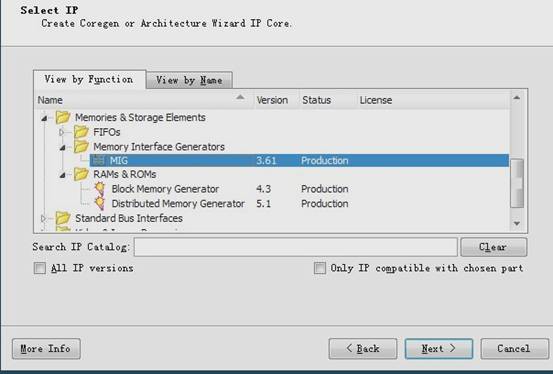

2、 选择版本,这里以3.6为例(尽量选择最新版本),进入Xilinx Memory Interface Generator界面,单击Next,进入下一步;

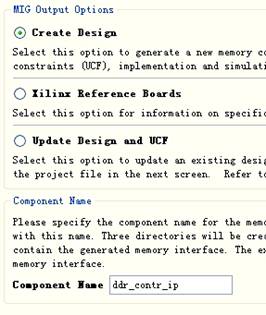

3、 选择输出项,输入自定义模块名;

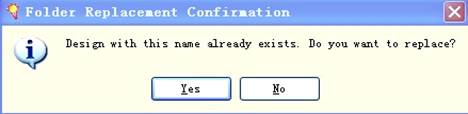

单击Next,注意:如果你是修改一个核而不是第一次生成核,会出现如下对话框,单击Yes,这时会覆盖掉一些文件,因此无论你在接下来的步骤中有没有对核的选项进行修改,最后必须点击Generator;

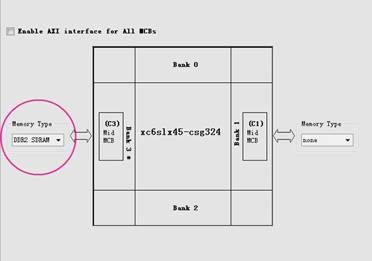

4、 单击Next,选择Memory Type;

注意到图中有个C1、C3,这是因为Xilinx的MCB有部分是属于硬核,引脚是固定的,分别存在于FPGA芯片的BANK1和BANK3,在代码中将看到很多的信号名是以C1_XXX和C3_XXX开头的,这很容易区分是哪个DDR芯片对应的信号名,注意与后面的端口(Port)混淆;

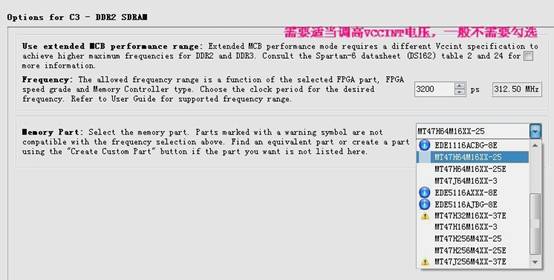

5、 单击Next,进入DDR2芯片选项模块,先选择存储器,再输入时钟;

这里的Memory Part 选择的是自定义的芯片,单击![]() ,输入一个自定义的DDR2芯片名,尽量输入芯片的实名而不是自定义名,这样有利于重复使用,不至于将来使用时不知所云,下面的参数可以在你所选的DDR2芯片DATASHEET中找到,输入参数值,保存,这样就可以在

,输入一个自定义的DDR2芯片名,尽量输入芯片的实名而不是自定义名,这样有利于重复使用,不至于将来使用时不知所云,下面的参数可以在你所选的DDR2芯片DATASHEET中找到,输入参数值,保存,这样就可以在![]()

找到自定义的存储器了,单击Next;

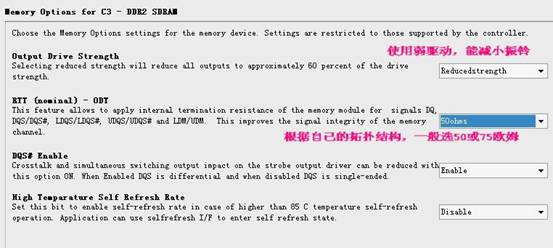

6、 选择同上,单击Next;

7、 设置端口的一些参数,主要是根据自己板子的实际情况稍微做一些修改即可。

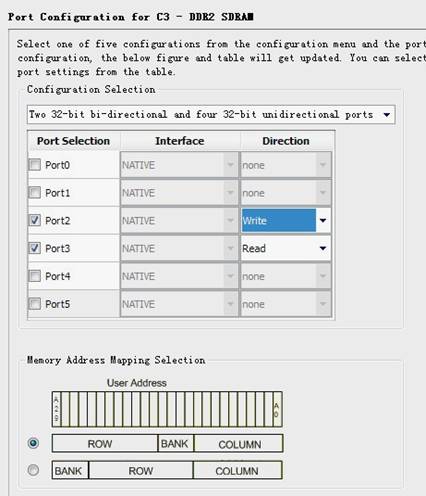

8、  进入端口配置,

进入端口配置,

(1)选择配置模式,单向与双向的意思是指端口是可读、可写,还是既可读又可写,

将端口配置成一个读一个写,其他不用;

(2)选择存储器的地址映射方式,可根据自己程序设计方便选择,这里默认;

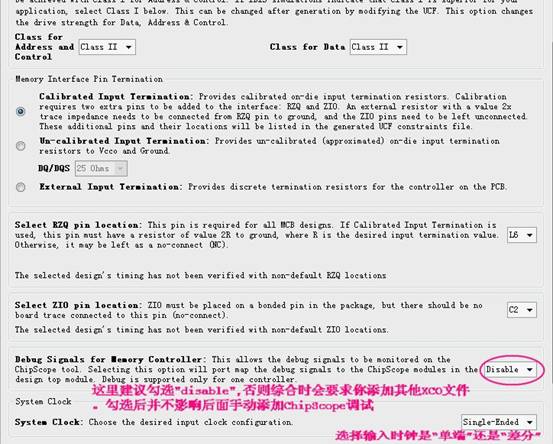

9、 Next;接着

10、进入FPGA选项,这里注意系统时钟的方式,根据实际情况选择单端还是差分,这里选择单端。还有就是要注意下这里debug选项,建议选择”Disable”.

其他默认;

11、Next,同上;

12、Next;

13、选择  Next;

Next;

14、Next;

![]()

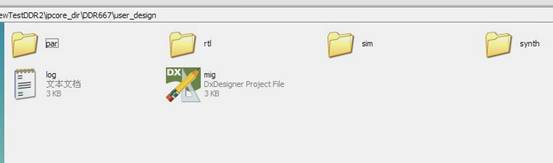

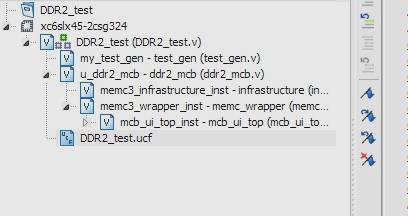

二, IP中的文件

打开生成的文件夹(一般在工程的ipcore_dir目录下),四个文件夹分别是参数配置、RTL代码、仿真库和综合脚本。

其中RTL文件夹内的文件是我们主要关注的。这里的DDR667(建立IP时取的名字)是顶层文件,另外两个分别是“管理时钟”和“管理端口”的描述文件。

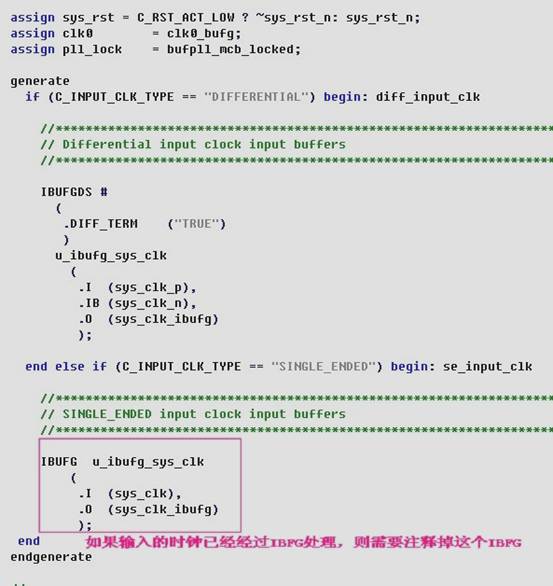

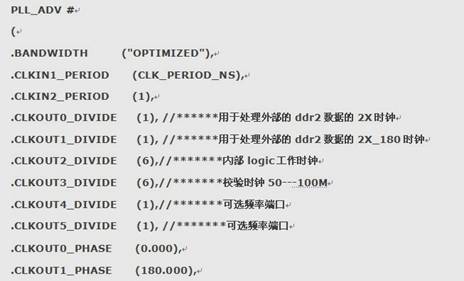

打开“管理时钟”的infrastrcture.v,需要注意的几点

(1) 如果MCB的输入时钟是经过IBFG处理的,那么这里的IBFG就需要注释掉,IBFG是全局输入时钟的缓冲,一个工程中有一个即可。

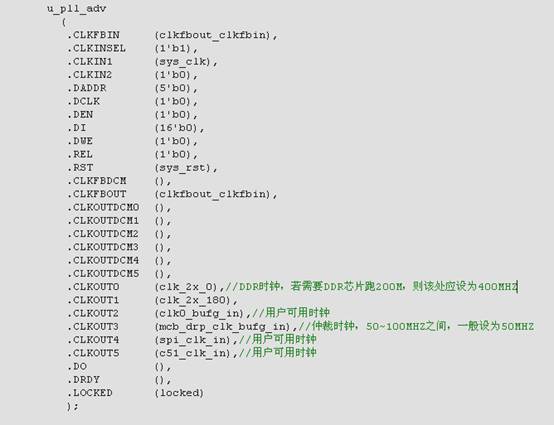

(2)u_pll_adv模块就是Xilinx的PLL核,并没有什么特殊之处,而MCB只用了其中的4个时钟输出,其中一个还是提供给用户逻辑使用,因此完全可以对该PLL的3个时钟输出做自定义,这样可以减少系统所用PLL个数。

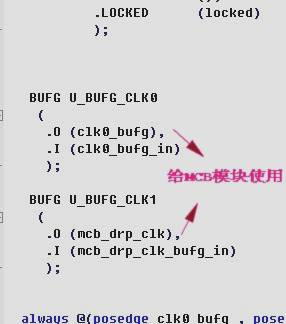

对于自定义的PLL输出根据需要最好加上BUFG,

然后将这些时钟添加到模块输出项,经顶层模块输出。

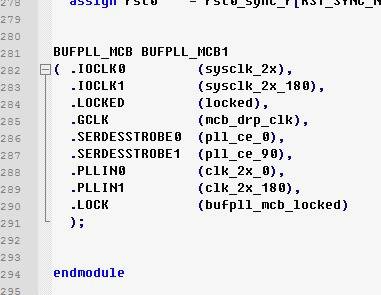

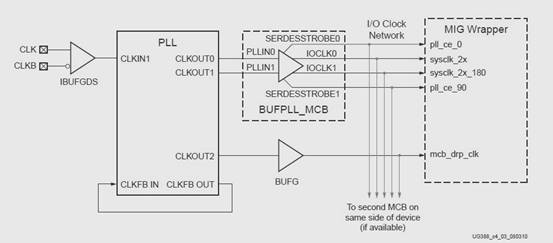

(3) 对于BUFPLL_MCB的详细解释,读者可参见ug382手册.输出文件和对应的关系图如下:

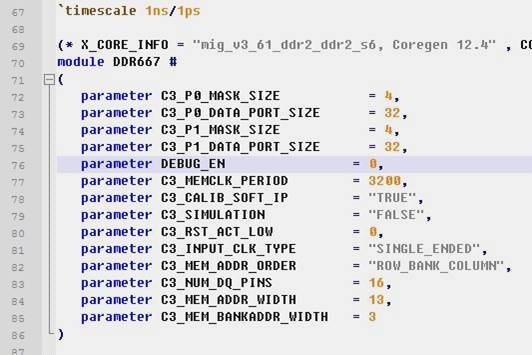

打开作为顶层文件的DDR667,可以看到在IP设置时所选择的参数都在这里了 ,如果需要做改动,可以在这里的parameter下修改。这里的参数有最高的权限,会覆盖所调用模块的默认值。

三, IP的使用

(1)在par文件夹下面有系统默认的UCF(约束文件),默认情况下会使用该UCF文件。

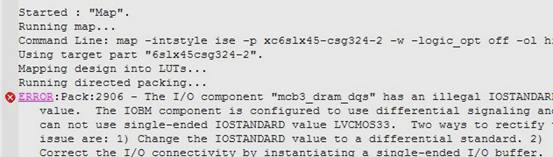

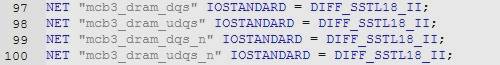

笔者在使用中发现一个奇怪的问题,就是在自己重新定义UCF,且确认所有的管脚都映射正确后,在MAP阶段一直报错,主要是报DQS、UDQS、DQS_N、UDQS_N这四个pin脚的分布有问题,尝试了很多办法都无效。

最终的解决办法是从工程中移除顶层的DDR2_test.XCO文件(备注:这里DDR2_test是笔者为IP所取的名字),手动添加所有的RTL源文件,编译后顺利通过map,不知道是bug还是其他的什么原因。

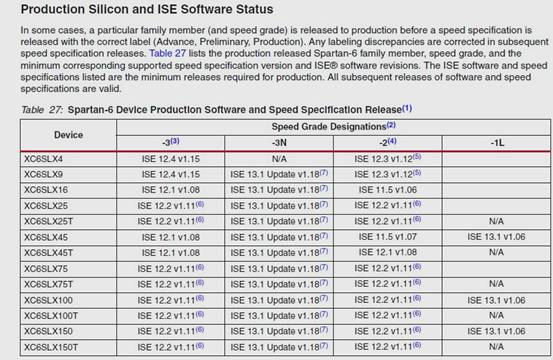

(2) 由于spartan6系统是最新的FPGA,xilinx官方一直在更新ISE软件,FPGA的内核也会有所变动,在期间选型时需要留意DS162文件中不同器件所需要的软件版本。

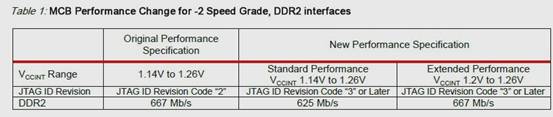

同时,对于使用-2速度的朋友需要注意下在XCN10024中XILINX队MCB的性能做了一些小小的修正,在内核电压较低(1.14~1.26)的情况下,速度由原来的667降低至625.

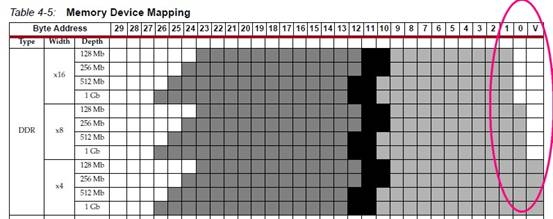

(3)由于系统默认是将整个DDR按8bit来重新对地址编码,这样对于X16、X8和X4就需要根据下图经行重新的映射,具体可以参看UG388

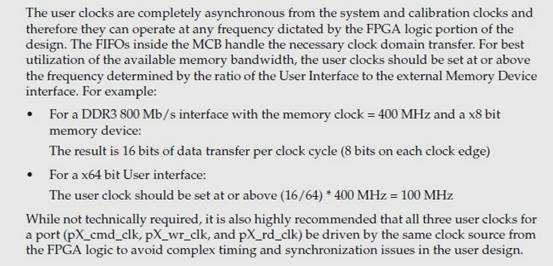

(4)在设置FIFO的位宽时,需要注意几个速度问题。比如DDR3-800,如果器件是X8模式的,那么每个时钟可以触发16bit数据(DDR是双沿触发),假设FIFO是64bit,那么系统时钟至少需要(16/64)*400=100MHZ才能跟上DDR的速度,同理如果是32bit的FIFO,那么至少需要200MHZ的系统时钟,这个在系统规划时需要注意。另外FIFO最多可以到64级,每一级大小等于位宽。

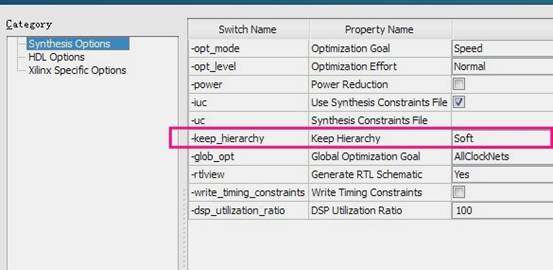

(5)由于整个IP中定义的参数和系统调用模块比较多,为了防止软件将一些信号优化掉,需要设置Hierarchy为soft

(6)如果系统中不止一个DDR,可以参考XAPP496中相关设计思路。

参考:

XILINX MCB使用详解 198610111sf@sina.com

Saprtan6硬核MCB读写DDR2实战篇 来源网络

/4

/4

用户377235 2012-5-18 11:47

写的很好,很实用,多谢LZ

用户404801 2012-3-23 10:23

用户391779 2008-8-1 15:12