`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 09:39:47 04/17/2009

// Design Name:

// Module Name: cordic_testbench

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

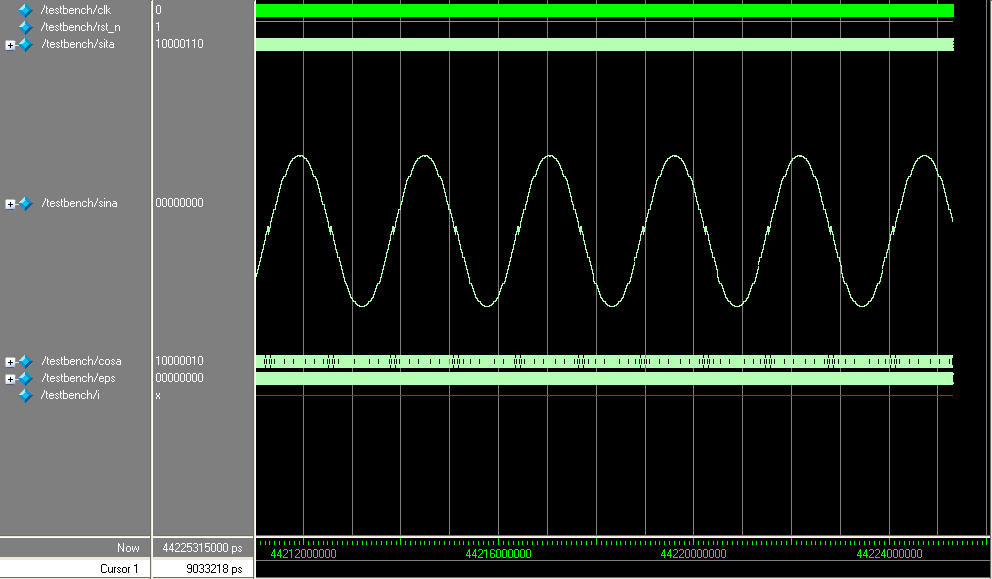

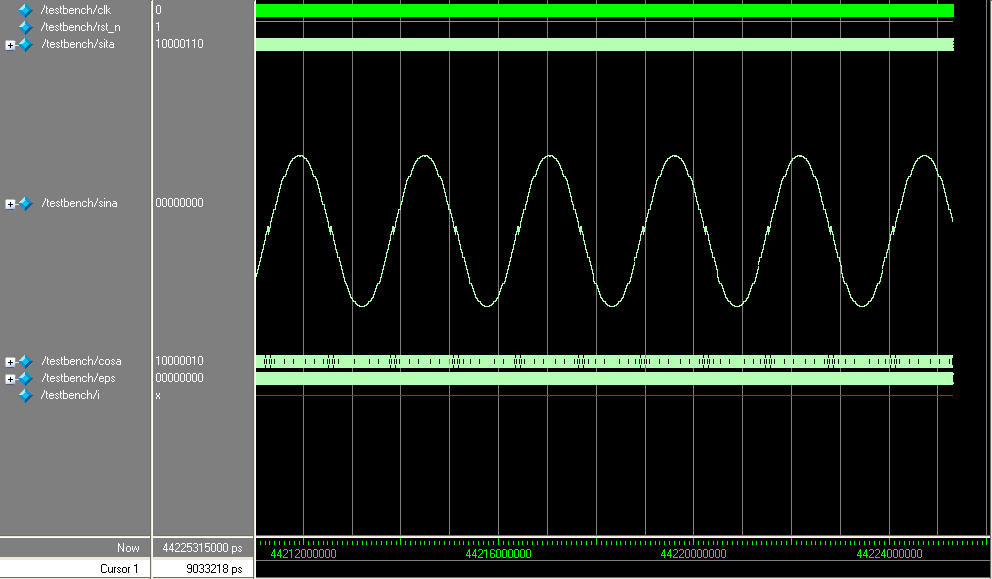

module testbench();

reg clk ;

reg rst_n ;

reg [7:0] sita ;

wire [7:0] sina ;

wire [7:0] cosa ;

wire [7:0] eps ;

reg [7:0] mem[0:255];

integer i;

cordic u_cordic(.clk(clk),.rst_n(rst_n),.ena(1'b1),.phase_in(sita),.sin_out(sina),.cos_out(cosa),.eps(eps));

initial

begin

clk = 1'b0;

forever clk =#5 ~clk;

end

initial

begin

rst_n = 1'b1;

#5

rst_n = 1'b0;

#5

rst_n = 1'b1;

end

always @(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

sita=8'd0;

else

sita=sita +8'd1;

end

endmodule

/4

/4

用户222327 2009-5-2 09:47