1引言

随着便携式消费电子需求的日益增长,低压、低功耗设计已经成为集成电路设计的研究热点之一。趋势表明[1],电压的降低给模拟电路设计带来很大挑战。就低压运放设计而言,一般传统采用互补差分对输入级以实现满幅度输入范围,然而,当电源电压低于Vt.NMOS+|Vt.PMOS|+VDS,PMOS-|VDS,PMOS|时,差分对会出现截止区,导致最小电源电压要高于2个阈值电压与2个过饱和电压之和。0.35μm工艺下Vt,NMOS的典型值为0.52V,Vt,PMOS的典型值为-0.75V,则传统结构的最小工作电压只能在1.4V左右。为了避免采用复杂工艺实现电源电压低于1V的运算放大器而增加产品成本。见文献[2-4]的电路结构采用共模电平偏移的电路结构,箝位共模电平,在标准CMOS工艺下简单地实现了低电压运算放大器。

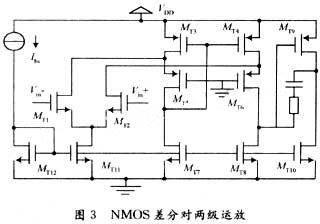

已有文献[2]采用PMOS差分对来实现电源电压为1V的运算放大器,但由于Vt,PMOS的典型值为-0.75V,使得前置反馈电路的工作电平范围为1-0.15V,几乎涵盖整个共模电平范围,运算放大器的稳定性降低,另外,该结构下的折叠式共源共栅结构也会受体效应的影响,影响增益的恒定性。本文采用NMOS差分对结构,还对前置反馈电平偏移电路进行相应的改进,使电源电压降为0.9V的同时,提高了增益的恒定性。

2 设计的基本思路

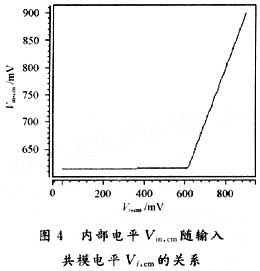

基于前置反馈的电平偏移电路的设计如图1,Vi+,Vi-的共模电平Vi,cm低于Vref时,通过反馈电路控制电流源获得适当的电流I,Vin+,Vin-的共模电平Vin,cm提升到Vref,同时电阻传递完整的差模信号,再由Vin+,Vin-连接NMOS差分对来实现整体电路,如图1所示。

|

3 运算放大器的具体实现

反馈电路的实现如图2所示,其反馈过程如下:Vi+,Vi-的共模电平Vi,cm降低时,Vin+,Vin-的共模电Vin,cm降低,此时IDM1减小,IDM11增大,Vx点的电位升高,IDM8增大,电阻的端电压增大,Vin,cm升高。若Vref过高,由于Ib的大小和电流镜工作电压的限制,Vin,cm不会上升到Vtel的电平。为了M5与M6,M7的漏源电压近似相等,引入M12增强电流镜的匹配。

|

下面对反馈环路的稳定性进行分析,运放A的开环增益为:

Av2=gmt9(rot9//rot10) (7)

其中,gmt1,gmt6,gmt9分别为MT1,MT6,MT9的跨导,rot4,rot6,rot9,rot10分别为对应MOS管的输出电阻。

|

|

|

/5

/5

文章评论(0条评论)

登录后参与讨论