多摩川旋变解码芯片周边电路的搭建

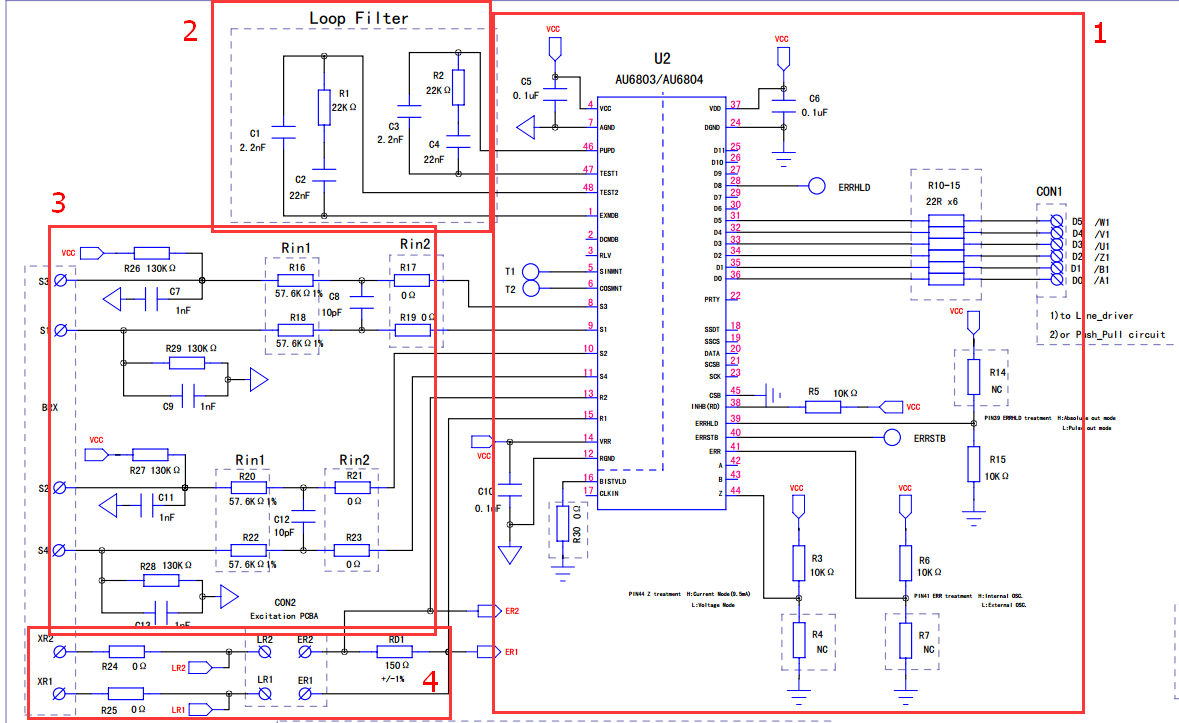

图1、AU6803/AU6804周边电路

备注:

红框1:基本配置电路

红框2:环路滤波电路

红框3:旋变信号输入电路

红框4:励磁信号输出电路

一、 基本硬件配置电路

1、 PIN 16 :BIST(自检测)功能开关。低:可执行,高:不可执行。可通过BIST功能实现断线自检测等功能;

2、 PIN 19 :SSCS 串行输入片选信号,低有效;

3、 PIN 21 :SCSB 串行输出片选信号,低有效;

4、 PIN 38 :INHB(RD) 串行数据读取锁存控制。低:信号锁存;

5、 PIN 39 :ERRHLD 错误状态保持。当运行过程中检测到异常时,该端口将输出高电平直至错误排除并复位。同时,该端口还是信号输出方式的设置口,在芯片上电瞬间,芯片将该端口置为输入,且监测其电平,当为高时,则设置芯片输出为绝对值输出方式,当为低时,则设置芯片输出为脉冲输出方式。该端口比较特殊,既为输出口,又为设置输入口,下面还有几个引脚也是这种类型的。

6、 PIN 40 :ERRSTB 错误复位。该端口可复位“ERRHLD(PIN39)”以及“ERRCD1~3(串行错误代码输出)”。高:错误保持,低:错误复位;

7、 PIN 41 :ERR 错误输出端口。当检测到异常时,该端口将输出1个高电平脉冲。同时,该端口还是晶振选择方式的设置端口,与PIN39类似,设置状态仅在芯片上电瞬间有效,高:选用内部晶振做为频率源,低:选用外部晶振输入做为频率源;

8、 PIN 44 :Z 。该端口同样为复用口,上电时做为励磁信号输出方式设置口,高:电流输出模式,低:电压输出模式。设置完成后,该端口变成Z相脉冲的等效输出口;

9、 PIN 45 :CSB 并行信号输出片选信号,低有效。

二、 滤波电路

1、 电源滤波

主要是通过靠近芯片电源引脚的电容来实现,这个电容通常取0.1uF。

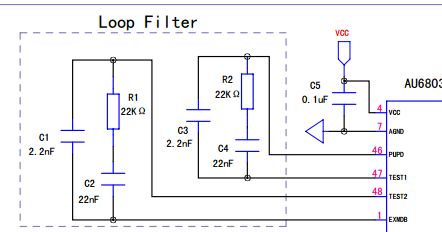

2、 环路滤波(Loop Filter)

该电路为执行R/D转换的关键组成部分,必须依下图所示进行配置,并且尽量避免引入其他噪声,否则R/D转换将受影响甚至不能正常工作。

图2、环路滤波电路

三、 励磁信号输出电路

AU6803/AU6804芯片内部自带励磁电路,可输出Iout = 9.5mA的励磁电流,在抗干扰要求较低的场合可直接使用芯片内部励磁而省略掉外部励磁电路。但是如果使用环境比较恶劣,则必须增加外部励磁电路,以提升其抗干扰能力。

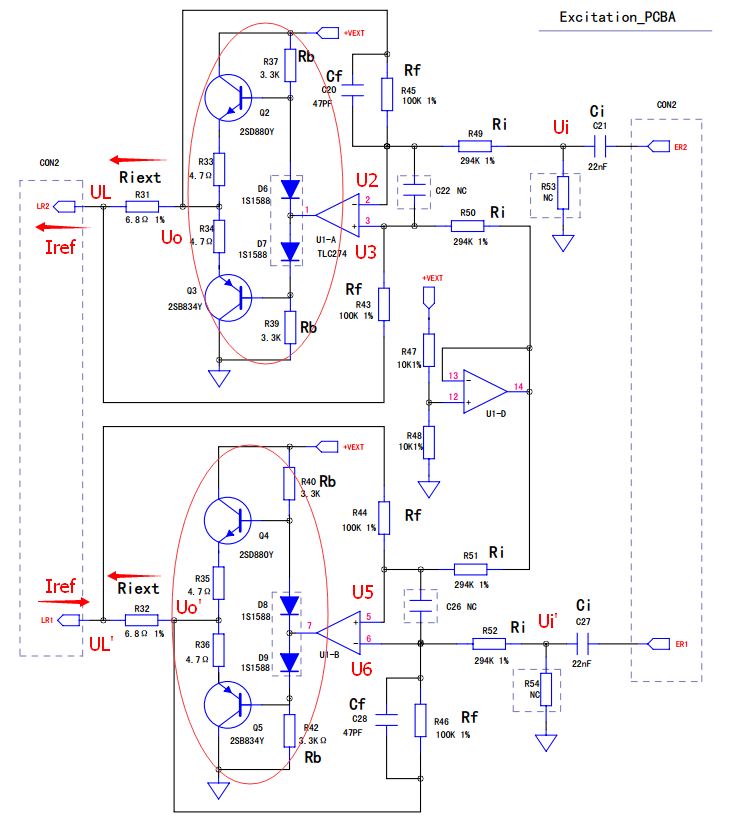

外部励磁电路参考电路如下图所示:

图3、外部励磁电路

针对该电路的分析如下:

1、 由图1红框4中所示可知,芯片端口输出励磁信号

;………………………………………………..1

;………………………………………………..1

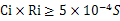

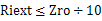

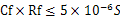

2、 Ci为隔直电容,依芯片规格书可知,Ri、Ci、Rf、Riext需满足

……………………………………………………………………………………………………………………….2

……………………………………………………………………………………………………………………….2

…………………………………………………………………………………………………………………………….3

…………………………………………………………………………………………………………………………….3

……………………………………………………………………………………………………………………………………….4

……………………………………………………………………………………………………………………………………….4

………………………………………………………………………………………………………………………..5

………………………………………………………………………………………………………………………..5

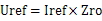

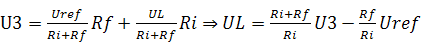

3、 设励磁电压峰峰值为Uref,励磁电流为Iref,旋变内阻为Zro,则

……………………………………………………………………………………………………………………………..6

……………………………………………………………………………………………………………………………..6

4、 如图3红框所示部分为典型的“甲乙类互补对称功率放大电路”,其中二极管D6~D9作用是消除交越失真;

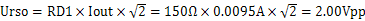

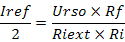

5、 由电路原理可推导得

………………………………………………………………………………………………………………………7

………………………………………………………………………………………………………………………7

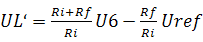

推导过程如下:

(1) 依初始条件可知

Ui = -Ui’ ………………………………………………………………………………………………………………………………8

…………………………………………………………………………………………………………………………9

…………………………………………………………………………………………………………………………9

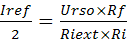

(2) 依运放“虚短、虚断”原理可得

U2 = U3………………………………………………………………………………………………………………………………10

U5 =U6…………………………………………………………………………………………………………………………….…11

……………………………………………………..12

……………………………………………………..12

同理可得

……………………………………………………………………………….………….13

……………………………………………………………………………….………….13

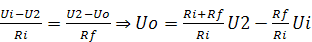

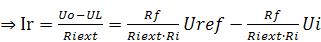

(3) 由叠加原理可得

……………………….14

……………………….14

同理可得

……………………………………………………………………..….…………15

……………………………………………………………………..….…………15

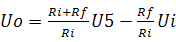

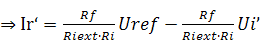

(4) 由10、12、14式 ……………………..16

……………………..16

(5) 同理,由11、13、15式 ……………………………17

……………………………17

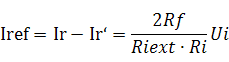

(6) 在负载处接入旋变,其阻抗为Zro,由于 ,故

,故

因Ui = Urso,故由上式可得

/5

/5

文章评论(0条评论)

登录后参与讨论