STM32 FSMC与FPGA 存储器接口 读写

panasonic.lin@163.com

FPGA通常作为协处理器,需要和CPU或DSP通信,我想在CPU端看来,

FPGA就是一块存储器,写入控制或者数据的寄存器执行命令,然后读取状态或者数据寄存器查询结果。

如果是应用NIOS II的话还方便,直接应用内置的Memory Mapped->Avalon总线就可以了。Quartus II内置的IP好像还没有

合适的,赛灵思XILINX起码还有。如果使用Quartus II的单双端口RAM,同步异步模式都很麻烦。

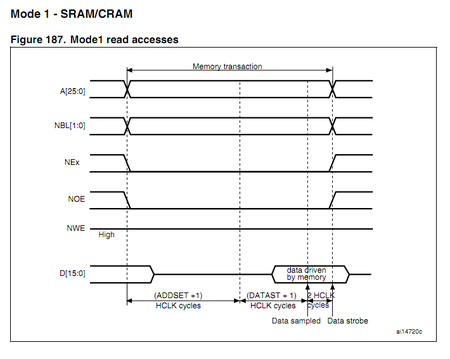

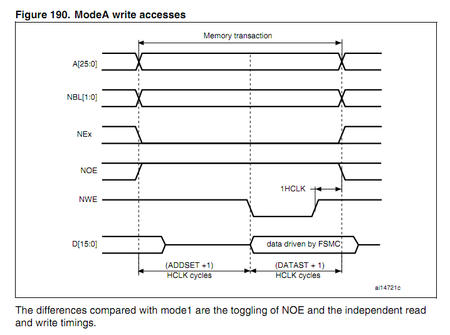

STM的异步存储器并行总线读写时序很简单,只需要处理nWR,nRD,nCS,AddressBus,DataBus,高低字节半字指示。

读时序(FPGA端):

1.nCS变低,进过地址总线建立时间后,nRD变低,采样解码需要的数据(根据addressbus),再

经过数据建立时间后,送出数据到databus,此前databus是高阻态;

2.databus一直保持数据到nCS变高为止,注意,不是nRD变高

写时序(FPGA端):

1.nCS变低,进过地址总线建立时间后,nWR变低,采样需要的地址(根据addressbus);

2.nWR变高时,采样Databus,根据前面采样的address,写入寄存器。

3.最后,nCS变高。

FPGA端的程序需要注意异步跨时钟域数据交换问题,同步方法可以参考edn特权同学的文章。

刚开始时,STM32端的FSMC接口程序没有设置好时序参数,把地址建立时间设置为0了,也就是说

FSMC 模式A和模式1变成一样了,nRD或者nWR一开始就和nCS一起变低。但是并不能说地址建立时间

就是真的为0了,还是有一段延时的,如果还是继续按在nRD或者nWR的下降沿采样地址总线,得到

的结果是亚稳态的结果。

最佳采样地址总线的时机是在nRD或者nWR下降沿后至上升沿这段时间的中点时刻。

/4

/4

用户1690702 2013-7-20 10:43

用户1690702 2013-7-20 10:28