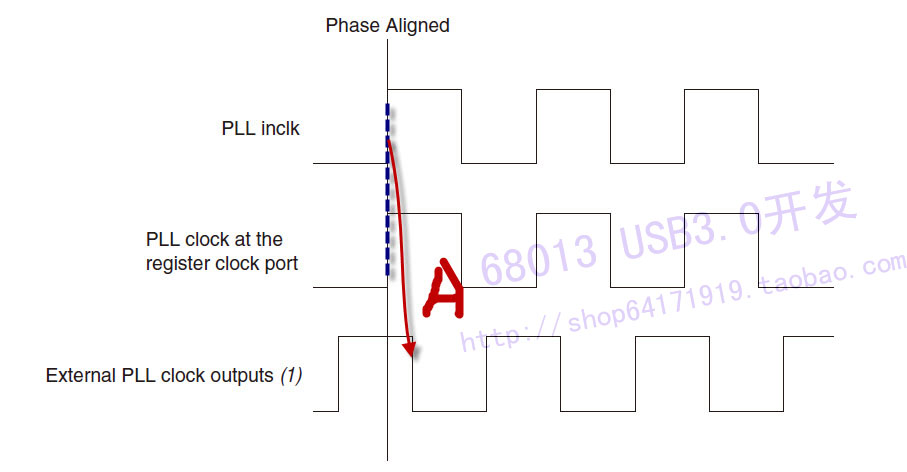

图中上数第一个波形为PLL inclk,一般是板子上有源晶振的输出,直接接到FPGA的时钟输入引脚上;第二个波形是PLL clock at the register clock port,代表的是经过PLL处理过的时钟,就是上一个帖子所说的C0、C1,一般接FPGA内部的全局时钟网络上,一般也不能从FPGA的引脚引出;最下面的波形是External PLL clock outputs,就是C2,可以供FPGA内部的全局时钟网络使用,也可接至引脚,供FPG**外的其它器件使用。

普通模式的特点是,C0和C1相对输入时钟来说,没有延迟(图中没有标记),但C2有延迟(上图中标记的A)。

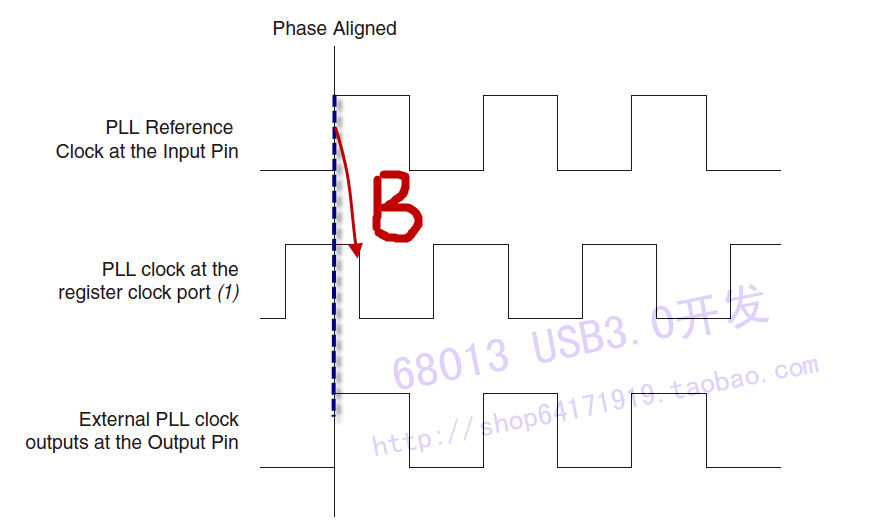

2、零延迟缓冲模式(Zero Delay Buffer Mode)

这种模式如下图,可以看出,C2与输入时钟没有延迟(图中没有标记),但C0和C1有延迟(图中标记为B)。这种工作模式与普通工作模式正好相反。

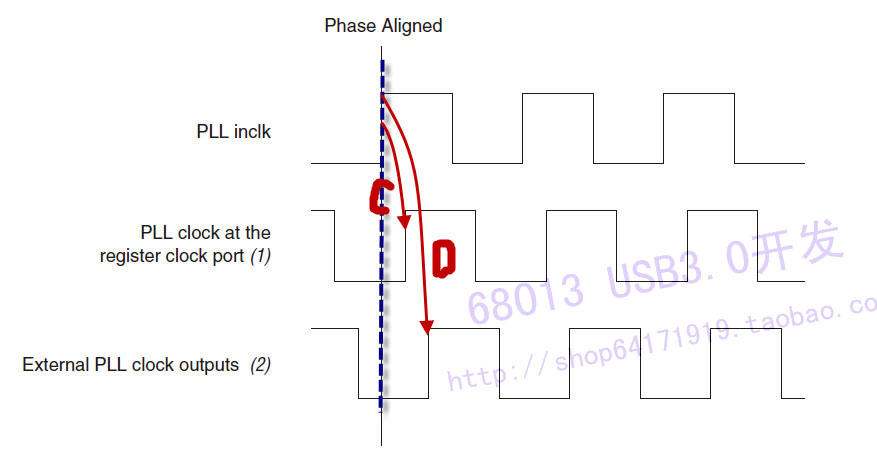

3、非补偿模式(No Compensation Mode)

这种模式如下图,C0和C1相对输入时钟有较小的延迟(图中标记为C),C2有较大的延迟(图中标记为D)。

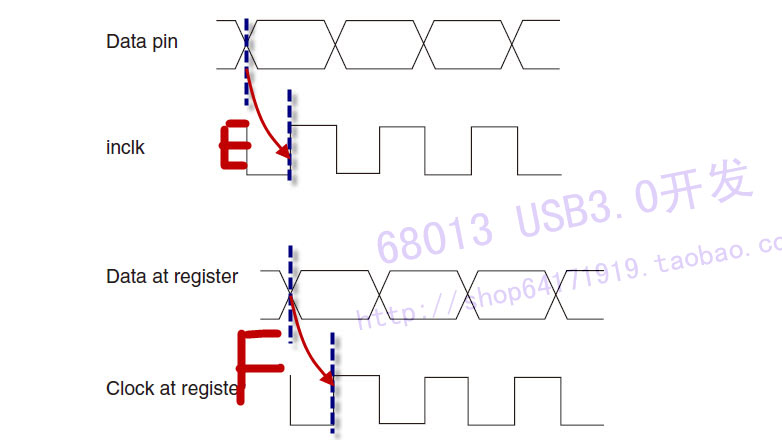

4、源同步模式(Source-Synchronous Mode)

这种模式如下图,输入到FPGA的时钟与输入到FPGA的数据有一个固定的相位关系(图中标记为E、F),经过PLL以后,这种相位关系不变,仅仅是有了一个延迟。

更多文章请访问:

我的博客1:http://bbs.ednchina.com/BLOG_liangziusb_440752.HTM

我的博客2: http://www.eefocus.com/liangziusb/blog/

EDN小组http://group.ednchina.com/GROUP_GRO_14600_3466.HTM

LZ3684 USB2.0开发板(CY7C68013A), 请访问我的淘宝http://shop64171919.taobao.com

LZ3014 USB3.0开发板(CYUSB3014),请访问我的淘宝http://shop64171919.taobao.com

实体店铺:北京新中发电子市场2557号

良子.2012年

欢迎交流:liangziusb@163.com

QQ:2687652834 392425239

/2

/2

文章评论(0条评论)

登录后参与讨论