感觉写的不错,方便自己一步步学习,特转来收藏!

1.写在前面

很早就想写这么篇短文,和大家交流学习的些许经验和心得。但一直有各种干扰,致使一拖再拖,这阵子赶上米国佬过圣诞,咱也忙里偷闲,赶紧把这篇短文码掉。。嘿嘿。

2.为什么要写

群里时常有新人呈周期性的问诸如,“我该如何学HDL?”,“非阻塞和阻塞有啥区别?”之类的问题。在此,笔者扯两句自己的学习体会,对这些问题一并予以回答。

3.English required

英文资料不一定能培养出优秀的FPGA工程师,但拒绝英文资料的工程师至多是个合格的工程师。

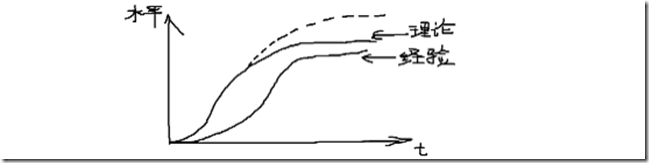

如图所示,纵轴代表综合水平,横轴代表时间,理论决定了由经验带动的水平提升的上限。而如果能经常参考英文资料,上限可以适当提高,如图中的虚线。

在一开始便强调英文的重要性是因为学习FPGA第一手的资料是大量的官方资料,如tutorial,user guide,cock book,handbook,application note,white paper等。

读者不能指望永远参考翻译的二手资料吧,何况很多还都严重脱节行业发展现状。

4.FPGA不是单片机

关于这点,很多人反复强调,但遗憾的是,把FPGA当单片机玩的人仍前赴后继。笔者琢磨着有可能是入门方法有误。

回想一下我们是咋学单片机的?买一本教材,了解一下IO口和控制字,然后开始画流程图,用C编程,做各种经典实验。

而当转到FPGA时,很自然的会借鉴“单片机模式”,买一本HDL的书,发现Verilog和C长还挺像,很轻松的啃完HDL,然后就开始“编程序”。待编完后,一点按钮,一口气从综合做到PAR(ISE和QuartusII都能一个按钮跑整个flow),然后仿真。仿真OK?皆大欢喜。不OK?改code。咋改?不清楚。

这个过程中最大的问题在于把FPGA最大的硬件本色当成黑盒处理:黑盒的输入是code,输出是仿真。

当把黑盒漂白成白盒,大致知道这盒子里有些啥,干了些啥,那在笔者看来才算是入门了。漂**是啥同志们应该猜到了:FPGA的结构。

推荐阅读:

a) 采用Cyclone与Cyclone-II系列器件进行设计.pdf

b) altera: Cyclone II Device Handbook.volume1

c) xilinx: ug380~ug389(spartan6)

5.HDL不是C,结构决定HDL

上面说到FPGA的结构是漂**,这节承接上文继续:

时序逻辑的敏感列表为啥只能有时钟和复位?如下:

always@(posedge clk or negedge rst_n)

而不能再加个使能:

always@(posedge clk or negedge rst_n or posedge CE)

也不能双沿触发:

always@(posedge clk or negedge clk)

也不能沿触发 + 电平触发:

always@(posedge clk or gated_logic)

这一切究竟是为啥呢。。

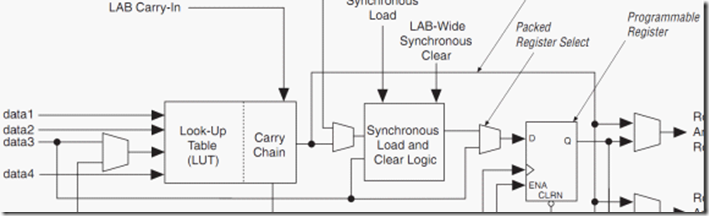

无他,结构如此。下图是cycloneII的一个基本单元LE(logic element):

右下角那个寄存器看到了吧,单沿触发,异步复位,同步使能。所谓结构决定HDL也。

顺便再看一下寄存器的复位端有个小圆圈,表示低电平复位,所以我们这样写:

always@(posedge clk or negedge rst_n)

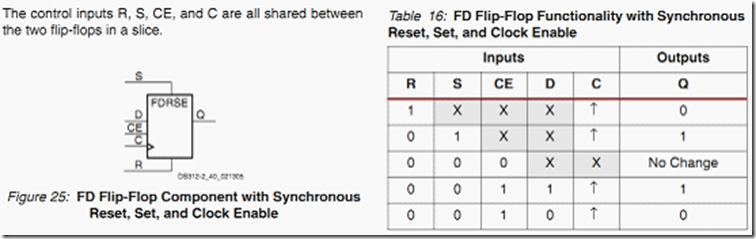

再截个spartan3E的:

看出点名堂了吧。xilinx的寄存器是高电平复位,所以如果你是xilinx用户,那就要这样写:

always@(posedge clk or posedge rst_n)

再来说一个经典的模型:FSM。为什么FSM推荐使用one-hot编码?如果读者有兴趣,可以做一个实验,会发现one-hot的解码电路一般都是小于4输入,也就是能用一个4输入LUT搞定。假设FPGA中的LUT是100输入,那即使解码电路再复杂点也能hold住了不是。

推荐阅读:

a) 设计与验证:Verilog HDL。

b) Verilog HDL 程序设计与应用 王伟编

c) Clifford E. Cummings的论文,http://www.sunburst-design.com/papers/

d) 大唐电信FPGACPLD数字电路设计经验分享

6.掌握主动权

由于综合器的算法限制,只有当我们的HDL满足一定的coding style,才能映射出我们想要的东西,比如前面说的对寄存器的建模对敏感列表的限制和要求。而有些复杂元件要求的coding style则更复杂,比如memory、乘法器。

这时更好的选择是直接调用软件提供的各种module,altera使用megawizard,xilinx使用core generator。这样不但直接告诉综合器我想要的是什么,把解释权掌握在设计人员自己手里,而且由于这些module一般都是经过优化(基于器件)后的网表,性能上会比自己写的更好,更灵活。

当然调用module也意味着在不同vendor之间转换将成为一个额外的问题。所以有些设计为了兼容各家的产品而故意不使用module。

到这里为止,经常是新人止步的地方,即所有的精力和视野都放在数字前端。要成为高手,后端的内容具有一票否决权。

7.综合(synthesis)与映射(mapping)

由于synplify廉颇老矣,外加两家vendor,altera有了自己的Qis,xilinx有了自己的XST,使得整个设计流程都已经高度集成化。集成化带来了方便,相对的也容易使刚入门的人犯晕。在此笔者不多做解释,直接上图比较,相信能说明问题。

***************************************************

module training(clk, rst_n, ce, ina, inb, outa);

input clk;

input rst_n;

input ce;

input ina;

input inb;

output outa;

reg ina_reg1;

reg ina_reg2;

reg ina_reg3;

reg inb_reg1;

reg inb_reg2;

reg inb_reg3;

reg outa;

always@(posedge clk)

begin

ina_reg1 <= ina ;

ina_reg2 <= ina_reg1 ;

ina_reg3 <= ina_reg2 ;

inb_reg1 <= inb ;

inb_reg2 <= inb_reg1 ;

inb_reg3 <= inb_reg2 ;

outa <= ina_reg3 & inb_reg3;

end

endmodule

***************************************************

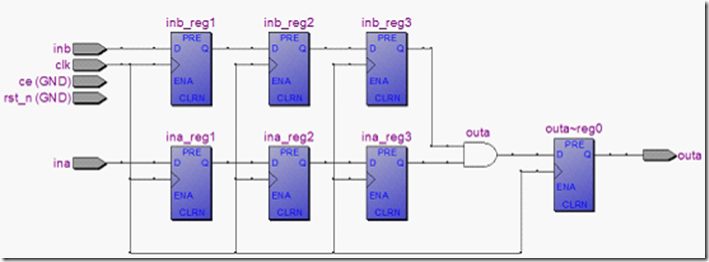

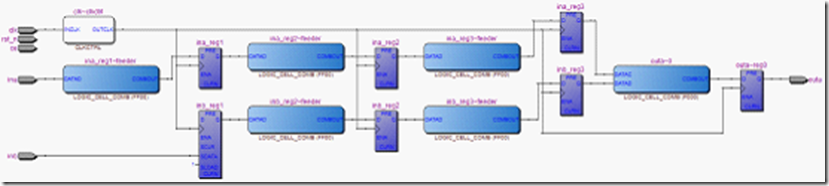

在altera中综合后:

映射后:

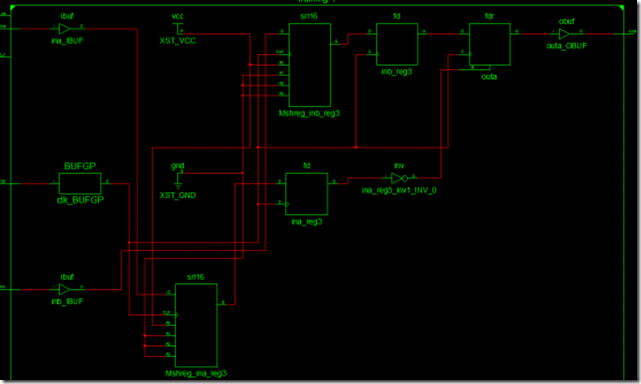

而同样的code在xilinx中综合后:

映射后:

可以看出两家vendor综合的结果是一样的,这时还没对应到具体的FPGA底层上,只是RTL级的网表。

但映射后就明显不同了,altera使用的是多个常规的寄存器,而xilinx使用的是SRL16移位寄存器(当然不是说xilinx就更好,只是这个特列更利于xilinx特性的发挥而已);并且出现了buffer和LUT,说明映射后的网表已经对应到FPGA的底层结构上了,这时才真正具有FPGA特色。

从映射开始便进入了非新人(不一定是高手,但一定不是刚入门的)的专属领域,即数字后端。

推荐阅读:

a) 逻辑综合器的故事

8.布局布线(place & route,PAR)

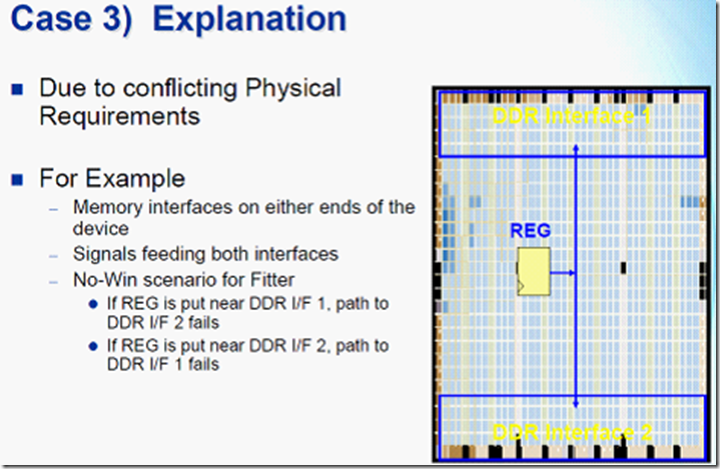

前几天有人问笔者:用chip planner看布局布线后的网表,为啥有些逻辑放得很近,有些放的远。

一般来说这个问题没有标准解,因为PAR具有一定随机性(seed,effort level等都会影响,甚至HDL中的一个小小改动都会影响)。当然也有一些常见的原因,比如:

上图的寄存器就处于左右为难,里外不是人的纠结状态。。

推荐阅读:

a) 2011.2.25_增量编译 by foreveryoung

9.时序

还有人还问了笔者一个问题,IO时序不太理想,怎么优化?笔者的回答是首先先做IO的register packing。而能这么做的基础是IOB中有一个寄存器专门负责处理这种情况的。还是那句话,如果了解FPGA的结构,这些问题将不再是问题。

说到时序,当然要说静态时序分析(static timing analysis,STA)。不是所有时序问题都需要做时序约束才能解决,但是不了解时序分析的基础知识,很多要求的coding style是无完美解释通的。

比如,都在说少用if-else,而要用case,为啥?答曰,因为逻辑层级少。那为啥逻辑层级少更好?

又比如,关于异步复位,大都处理成异步复位同步释放,那么为什么这种结构能有效解决亚问题的问题?

再比如,有些初学者不习惯使用PLL,而喜欢用寄存器计数分频或者门控信号作为时钟,即通常所说的ripple clock和gated clock。为什么在FPGA设计中不推荐这两类时钟?

如果有时序分析的基础,这些问题能得到很直观的理解和体会。

第八点和第九点只是告诉刚入门的新人,有这么个东西,等入门了以后表忘了有这么个领域需要攻克。

推荐阅读:

a) 通向FPGA之路---七天玩转Altera之时序篇V1.0

b) 时序优化实验部分 V1.0 by foreveryoung

9.广告

以下是我做的一些笔记。

a) 2011.2.25_增量编译 by foreveryoung

b) Netlist Viewer by foreveryoung

c) 通向FPGA之路---七天玩转Altera之基础篇V1.0

d) 通向FPGA之路---七天玩转Altera之时序篇V1.0

e) 通向FPGA之路---七天玩转Altera之验证篇V1.0

f) 状态机设计 by foreveryoung V2.0

后记:

上文提出了很多为什么,笔者没有直接给出答案,留给读者自己探索了。如果想就这些问题进行进一步交流,请加群:91968656。当然,除去因相关理论不足导致的问题,很多时候当有疑问时,首先因做的是自己尝试,然后通过观察RTL viewer或technology map viewer,仿真等手段验证。所谓大胆假设,小心求证。

好了,笔者原还想扯一下优化,但转念一想,已经扯了九点,九乃大数,便作罢。而且一次扯太多容易让人产生疲倦感。故本文到此为止。下次有机会再补充。

完

2011.12.25

foreveryoung

上海

用户832726 2015-8-10 09:29

用户1014538 2015-7-24 08:09

jan_258_715267317 2015-7-21 08:51

用户1578945 2015-7-11 14:52

用户1707279 2013-12-29 13:00