尽管目前围绕着领先硅晶圆代工厂的热点话题都是如何在14nm节点从平面晶体管转换到finFET结构,但来自美国的半导体产业观察家 Mark LaPedus 日前撰写博文称,半导体设计和制造在20nm节点将面临5大挑战。

GlobalFoundries、Samsung、TSMC和UMC都在加快步伐以期在14nm节点采用finFET工艺。这似乎走得有点过快了,就像有些专家警告的,目前仍然有大量的IC设计和制造方面的难题困扰着20nm工艺。代工厂在28nm和20nm继续使用平面工艺,到14nm才考虑转移。部分代工厂仍在继续提升他们28nm工艺的高K/金属栅方法,而供应商认为在28nm仍存在各种挑战,到20nm 形势更艰巨。就像Cadence的硅实现部门定制IC研发部副总裁Tom Beckley说的,20nm会是一个全新的突破性的世界。

20nm节点,既有涉及到经济因素,即晶圆厂、工艺和设计成本,也有技术挑战,例如双重图形的到来、严重的版图相关效应,以及在设计中引入的新的第三层进行原位互连。这个中间层有可能是IC流程中一个“破坏环节”,GlobalFoundries的DFM/CAD和研发部主管Luigi Capodieci这样评价道。

由此,Mark LaPedus总结出了20nm世代的五大挑战,如下:

1. 经济因素使得少数派生存

芯片微缩使得器件更小,成本更低,但是也附带了一些主要的不利影响。只有少数财大气粗的公司才玩得起20nm,设计和制作越来越昂贵,这些公司每天都在**。

引用研究机构IBS的数据,在32/28nm节点,晶圆厂运营成本为30亿美元,工艺研发成本为12亿美元,IC设计成本大约在5千万美元到9千万美元之间,掩膜版成本为200万-300万美元。

而在22/20nm节点,晶圆厂运营成本为40亿到70亿美元,工艺研发成本为21亿-30亿美元,设计成本上升至1.2亿-5亿美元间,掩膜版成本则达到500万-800万美元。

另外还有些数据可以佐证成本的急剧上升,EDA工具成本从32/28nm的4亿-5亿美元上升至22/20nm的8亿-12亿美元间。另一个令人头疼的趋势是验证,验证用时也会爆炸性的增长。

有什么好的解决方案呢?过去,电路设计者和版图工程师往往是互相独立的。而现在,这两个部门需要紧密合作,来处理未来更为复杂的局面。

2. 双重图形进入视线

IC产业对193nm光刻技术的运用远远超过了最初的预期,几乎达到了极致。令人惊奇的是,在32/28nm逻辑前段,IC产业仍在使用基于单次曝光的193nm浸没式光刻扫描机。

由于各种下一代光刻技术候选方案的推迟使用,如EUVL,20nm节点产业还必须依赖于193nm光刻和多重图形技术。当前,东芝和SanDisk还在用193nm扫描机制作19nm的NAND器件,并采用了分辨率增强(RET)技术和自对准双重图形。与此同时,在22nm节点,英特尔也在采用193nm浸没式光刻和双重图形技术。

双重图形涉及到采用两个掩膜版在同一层上进行分别曝光,因此,增加了复杂性和芯片制造成本。在20nm,代工厂可能都会采用包含光刻-刻蚀-光刻-刻蚀(LELE)的双重图形技术。套刻可能导致局部线宽变化或局部关键尺寸(CD)的变化,从而引起电性能的退化。

3. 新的布线层

在28nm及更高节点,制造流程分为前段工艺(FEOL)和后段工艺(BEOL)。前段包括晶体管和逻辑电路的制作,后段则处理通孔、互连层和其他结构。在20nm,晶圆厂则正在讨论第三层互连。这一层也会成为制造流程中的另一挑战。因此,行业需要新的方法来解决新的布线层,Cadence的Beckley这样指出。

4. 严重的版图相关效应(LDE)

Beckley还指出,预计在先进节点会看到严重的版图相关效应。浅沟槽隔离(STI)以及邻近效应(WPE)是两类版图相关效应。因此,厂商在IC设计阶段就要处理掉这些寄生效应。

5. 更多的DFM挽救措施

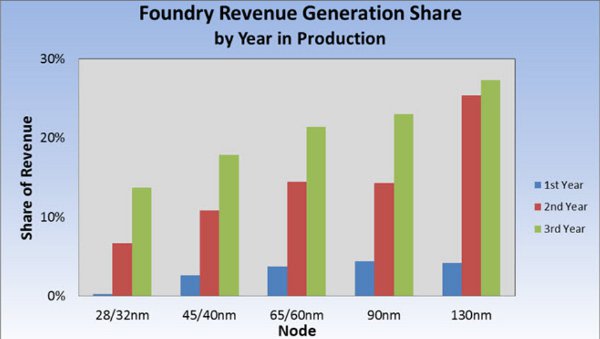

摩尔定律放慢了步伐?答案:对于存储器和处理器IDM是否定的,对于代工厂那是绝对的。VLSI Research总裁G. Dan Hutcheson表示,更要警惕的是,从130nm以后,代工厂转换制程的能力和设备投资回报率一直稳步下降。130nm的意义在于,工艺和设计开始紧密关联,此后便有了DFM(可制造性设计)的兴起。

晶圆代工模式在分崩离析?

“这个图表更让人可怕的是,这种下降是可以预见的稳步下降。”Hutcheson说,同时,领先的fabless公司如Nvidia 和Qualcomm 都很明显地关注于他们的代工厂是否有能力跟上摩尔定律。要想继续参与这场游戏,还得持续降低每晶体管成本。要说有什么问题的话,这张表对于我们以前公认坚不可摧的fabless+foundry模式提出了质疑。

解决方案是什么? EDA工具商、代工厂和fabless必须紧密合作,但是一旦代工厂不再受信任,那可以确认的是:如果问题得不到解决,产业将会发生重组洗牌。面对这种警告性趋势,fabless也有很大的压力,需要开发出更稳健的设计,确保设计能够最及时地生产出来。为了解决这种挑战,近期芯片厂商开始依赖于DFM。作为DFM的一部分,芯片良率和良率提升工艺变得更加重要。

/2

/2

文章评论(0条评论)

登录后参与讨论