电子竞赛总结

广西区的电子竞赛过去有几天了,又是一个阶段性的时间结束了。我自己也好久没上EDN逛逛了!前面一大侠给我说,是是,那EDN上高手多,建议我多看看。这句话说得对啊,至于你们信不信,反正我是信了!

读大学前面两年,虽也听老师说过,师兄“吹”过,说每个技术人员,最好都要有一个博客,这样能把自己的学习历程,经历,体会记下来,在写的过程中,算是自己的一个总结、、不断积累。嗯,对,说得是!可是,到现在我也没看到实验室里面真正有几个同学去找个地方“安家”写写自己的东东!还好,我现在算是慢慢的体会到了这玩意的好处啊(里面大侠的资料,经验,行业发展,搞得我跳出了那口井,更加热爱这个行业!!)。真的需要这样做,因为很多东西你经历了,然后,然后,晕,就这么完了,什么都没留下!不,留下了残留在脑海的残缺的记忆!这样我觉得就好可惜了,很多东西,我学习过了,我做过了,我的小小成果,我干嘛不好好整理好保存,不断积累起来啊?

只有当你去“逼”着自己去敲点儿字,写点文字,图片,资料总结的时候,当你不知道写什么,又不能乱写的时候,你总会去想想这事情的经过和当时、现在自己的想法,这样一来,你就会发现,是啊,原来不去想,我就会错失好多我没注意的东西,没注意的细节啊!!

这里面有两点,第一是:积累;第二是:细节! 对,就是它,这次竞赛我首先出问题就在这里面了!!

边想边写到这里,我发现我这理科生的水平,弄些文字的东西,总是感觉有点儿不对劲,觉得很多地方用语不合适,可我又憋不出什么好的词,还好,还好,这些东西也就我自己随便看看,心里的真实反映罢了,无关紧要啊!

(男人,要对自己好点儿,搞我们这行,现在在学校天天都这样了!出去要是遇到个项目,做不出来,那不得天天熬夜啊?女朋友就没得找啦!!好吧,会宿舍去,睡觉咯,明天继续!凌晨10分,先回去了)

接着继续写吧、、

正是RLC测量仪的,他的方案和我们当时用的没什么差别,听他说,他们的作品还是做得蛮好的,都达到了题目的要求,但是很遗憾,我们的作品很多地方问题很多,在此我不得不佩服他的实力!现在想想,的确,我们没把作品做出来很正常,因为我们太多的细节没搞清楚,也不知道具体怎么去实现,出现了问题,分析原因也不透彻,更不能解决问题了!

所以,我们失败在平时的积累和细节上面了!先是我们的方案,在理论没搞清楚和具体怎么实现之前,急急忙忙把前端电抗-矢量电压转换的pcb画了出来,后来一测量发现由于没有加入标准电阻量程的转换(先用的固定标准电阻),在不同的电抗元件接入时,采样的Ux几乎是不变化的! 这就要命了,前端采样的电压都变化不大或者几乎没变化,那何来后面的鉴相和转换?这是一个问题、、

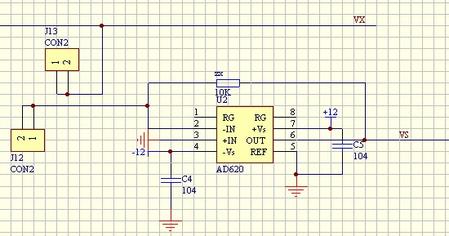

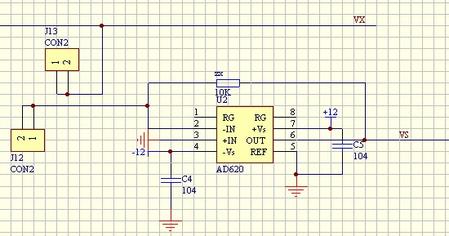

如图,可以看出,理想运放我们采用的是AD620,那个10K的电阻,正是我选择的标准电阻,而J12,J13,就是接口端子了,是接入待测的电抗元件的,当时我们真的没多想是这里需要量程标准电阻的转换,后来测试板子的时候就发现问题了,这样采样得到的ux变化是很小的!

后来,出现的问题是,我们开始采用的信号源,是用的以前我们做过的AD9850产生的测试信号,它本身倒是没有什么问题,信号稳定,频率方便可调,有效值也可以调到0.6V,

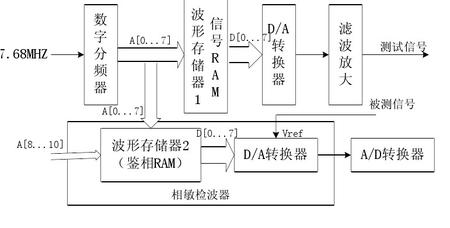

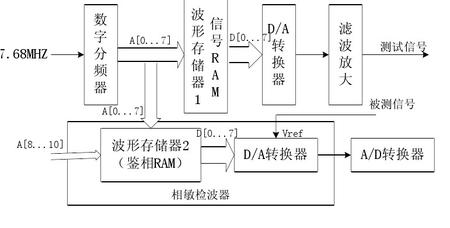

但是后面如果用数字鉴相,那就有问题了,那就是如果不采用FPGA加DA转换的话,那样生成波形的数据就无法拿到,这样也就无法复制一份到鉴相器的RAM中,更无法产生与被测信号一致的频率了,这是致命的,因为9850里面的数据是固化的、、

从图中可以看出,前面产生的测试信号的分频数据必须一致的复制一份到后面的RAM中,因为鉴相系统要求信号源频率和相位基准信号的频率严格一致!所以用9850固化的死路一条!(关键是时间矛盾问题!!后面再来换FPGA进去,时间不多了啊,总共四天三夜的时间,经不起到处出问题调整,是经验不足?分析不够??)

后面还出现了一系列大大小小问题,这里不堪回首啊!!

说白了,就是平时东西做得太少,也没做过这方面的题目,所以实际实现起来往往捉襟见肘啊!暴露出来的问题实在太多、、

整个比赛的流程,我相信经过这次,咋也算是明白了很多,怎么把握时间进度,怎么确立可行的方案?怎么分配人力资源,等等问题可都是要一个小组去思考解决的问题啊!

现在回想起来,每天就睡两个小时真的不好受,不过再辛苦,到头来,还是让自己很难过,倒不是因为结果和什么奖,只是因为发现自己还是只懂皮毛而难过!!

做技术,没那颗心不行;静不下来,不去钻研、研究更不行!!

细节!越细的东西,越能体现出水平!

积累!冰冻三尺,非一日之寒!

原来真正的比赛,是在赛前啊!!

我相信,电子竞赛不会使我迷茫和丢失自己一生想学习的方向,只会提醒自己,提高自己,检验自己!

/5

/5

用户1707737 2012-10-12 20:09

谢谢,正在做这个题目,做完了,还会把跟详细的贴出来

用户403664 2012-9-28 11:47