TX 复位案例

一、 TXOUTCLKSEL = TXOUTCLKPMA

这种情形下,TXOUTCLK 的频率是(LINE RATE)/(INTERNAL DATAWIDHT),它会随着线速度的变化而变化。

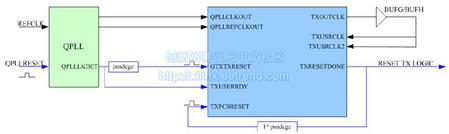

对于 7 系列 SERDES,内部位宽可以有 16/20 bit (即 2 字节)和 32/40bit(即 4 字节)2中选择。跟逻辑接口的外部位宽有 2、4、8 字节 3 种选择。由于逻辑可以跑到 368MHz以上。所以对于大多数的应用,TXUSRCLK/TXUSRCLK2 是可以同频的。此时,其时钟框图就会如下:

这种复位方案里,有一些要求:

SERDES 工作在顺序复位模式下(工具产生的代码默认模式)

RESETOVRD = 1’b0

GTRESETSEL = 1’b0

QPLLRESET 或 CPLLRESET 需要脉冲复位

至少一个参考钟周期

QPLLLKDET 或 CPLLLKDET 的上升沿上产生 GTXTXRESET 脉冲,启动 SERDES 进入顺序复位

同时,把 QPLLLKDET/CPLLLKDET 连到 TXUSERRDY

最好能延时 2~3us 以保证 TXOUTCLK 稳定。

在 TXRESETDONE 的第一个上升沿做 TXPCSRESET 的复位

对单路应用不需要这个复位。

对于多路需要对齐输出的应用,需要把所有 TXRESETDONE 都拉高后做TXPCSRESET 复位以减少各路的输出偏移

二、TXOUTCLKSEL = TXOUTCLKPMA,用到 MMCM

这个和上面一个的差别就是需要用到 MMCM。由于 MMCM 的输入是 TXOUTCLK,必须等到 TXOUTCLK 稳定后才能释放复位;而 MMCM 给 SERDES 提供 TXUSRCLK 和TXUSRCLK2,所以 TXUSERRDY 必须在 MMCM 稳定后才能拉高。

同样,对于多通道应用,需要在所有 TXRESETDONE拉高后给一个 TXPCSRESET 脉冲,这样可以减少发送数据通道间的偏移。

三、TXOUTCLKSEL = TXPLLREFCLK_DIV1/2

这种应用和第一种不同之处在于TXOUTCLK的时钟来源不同,这里是来自于参考钟。所以它会在 QPLL 锁定之前就稳定下来。当然我们还是可以借用第一种复位方法。只是QPLLLKDET/CPLLLKDET 送到 TXUSERRDY 时不需要延时去等待内部时钟稳定。

四、TXOUTCLKSEL = TXPLLREFCLK_DIV1/2,用到 MMCM同样,这种应用可以参考第二种。

当然由于 MMCM 的输入时钟是参考钟,所以它的复位释放也不需要等待 PLL 锁定。所以我们也可以用下面的复位方法

当然由于 MMCM 复位要求,QPLLRESET/CPLLRESET 的脉宽需要大于 3 个参考钟周期。

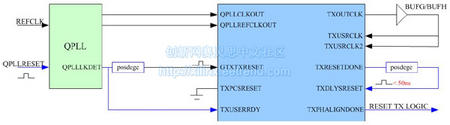

五、TXBUFFER BYPASS 情形

对于 CPRI 等有延时精度要求的应用,需要把 TXBUFFER 旁路。这时需要在上面的复位之外还要有相位对齐电路的复位。

要能进行相位对齐,对时钟有一定要求:

1. 同源同频。这里只是做相位对齐,频率必须相同;

2. 时钟稳定。只有时钟稳定后才能进行相位对齐操作。

所以相对于前面使能 TXBUFFER 的应用的复位,在 TXRESETDONE 拉高后,做一次相位对齐操作就可以了。

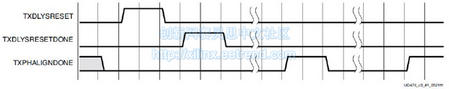

这里需要注意的一点是,TXDLYSRESET 的脉宽必须小于 50ns。

整个复位的波形图如下

和前面不同的是,这里用 TXPHALIGNDONE 作为后续逻辑的复位信号。这是因为这个信号拉高了,表示 SERDES 的初始化已经完成,可以工作了。而前面的几种应用,TXRESETDONE 的拉高是 SERDES 能够正常发送数据的标志。

/5

/5

文章评论(0条评论)

登录后参与讨论