专家秘笈连载三:7系列GTX的复位设计

前言

随着半导体技术,特别是 FPGA 的发展,单片芯片的处理能力越来越强。现在单片的处理能力都在 1Tbit 以上。而要处理这么多的数据,单靠原来的 LVDS, LVPECL 已经无法满足芯片接口吞吐量的要求。所以,如今越来越多的应用都用到高速 SERDES。

XILINX 的 SERDES 作为业界翘楚,越来越多地被客户接受并广泛应用。而随之而来设计、调试问题,也是让客户感到害怕的问题。特别是客户容易对高速 SERDES 犯怵,碰到问题又无从着手,导致进度受阻,压力倍增。

这是我着手总结 SERDES 设计调试的初衷。

这次主要讲 SERDES 复位设计。

复位的作用

众所周知,现在主流的 FPGA 上实现的都是时序逻辑。时序逻辑有一个特点就是前面的状态会影响到后面的状态。所以在这种应用里,初始状态的确定是整个设计里非常重要的一个环节。复位就是用来初始化逻辑状态用的。

对于 SERDES,根据不同的应用,其时钟方案是不同的。对此,SERDES 的状态,特别是BUFFER 的状态会受到很大的影响。由于 BUFFER 的读写时钟有效稳定的时间不同,大致会引起以下 2 种情况:

1. BUFFER 上下溢出,使得输入输出误码;

2. 多通道应用里,通道间引入偏移,使得各路通道绑定失败。

所以复位设计必须小心,特别需要和时钟方案相匹配,才能给可靠的设计打下良好的基础。

7 系列 GTX 的时钟结构

上面说到,复位应该和时钟方案相匹配,所以在这里简单介绍一下 7 系列 GTX/GTH 的时钟结构。

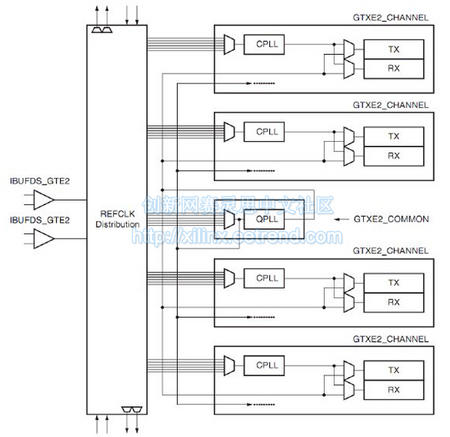

7 系列 SERDES 是以 QUAD 为单位的。在一个 QUAD 里,有

a) GTX/GTH: 一个 QUAD 里有 4 个 SERDES;

b) 2 个参考钟:它们可以连到任意一个 PLL 上。而且可以给上下相邻的 QUAD 提供参考钟;

c) CPLL:这是每路 GTX/GTH 都有的 PLL。这个 C 是指 Channel;

d) QPLL:每个 QUAD 内的 SERDES 共享的 PLL。这个 Q 是指 QUAD。

QPLL 和 CPLL 可以供到每个 SERDES 的发(TX)和收(RX)。在 SERDES 里有TX/RXSYSCLKSEL[1:0]端口选择使用哪个时钟源。

复位设计的案例

下面,根据不同的时钟方案,会列出一些复位的方法。

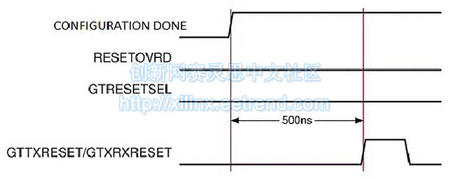

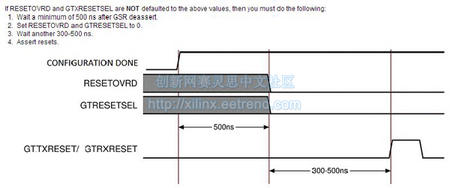

首先需要提醒的一点是:对于 7 系列的 SERDES, bit 文件下载完(CONFIGDONE 拉高)后的500ns 时间内的复位是无效的。SERDES 需要的复位是脉冲。所以 FPGA 配置完成后 500ns 后复位信号才能拉高。

如果在 500ns 之前就拉高,那是无效的。需要在后面在有一个正脉冲才行。

关于这个问题,在 XINLIX 官网上有 AR43482 作说明。

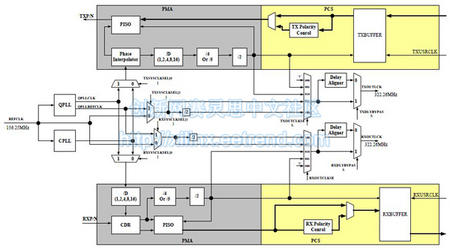

另外相对于以前的 SERDES,在 7 系列 SERDES 里多了 2 个信号:TXUSERRDY 和 RXUSERRDY。

这 2 个信号是用来控制何时进行 PCS 复位的。

SERDES 的顺序复位是指 GTXTXRESET 或 GTXRXRESET 有复位脉冲时,SERDES 会进行从 PMA一直到 PCS 的复位,最后把 TXRESETDONE 或 RXRESETDONE 拉高。

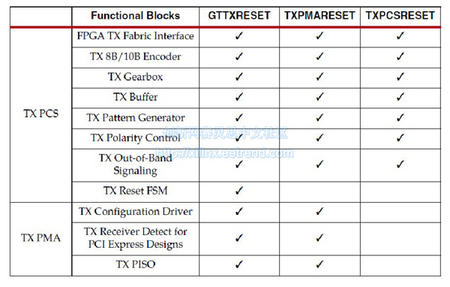

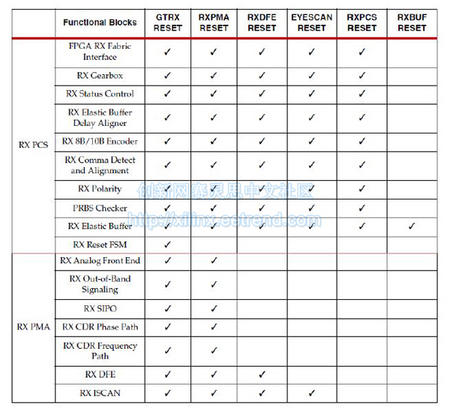

PMA 和 PCS 复位涵盖的范围见下表

整个复位顺序都是从 PMA 到 PCS 的。具体流程可以参考 UG476。

在完成 PMA 复位后进入 PCS 复位是,TXUSERRDY 和 RXUSERRDY 就是开关。只有当它们为高时才能进入 PCS 复位,继而完成整个 SERDES 的复位。TXUSERRDY 和 RXUSERRDY 的含义是用户钟 TXUSRCLK/TXUSRCLK2 和RXUSRCLK/RXUSRCLK2 都稳定了。这个时候可以进行 PCS复位了。

/2

/2

文章评论(0条评论)

登录后参与讨论