P20

System Synchronous Output 系统同步输出

这部分描述的约束命令是 create_clock 和 set_output_delay

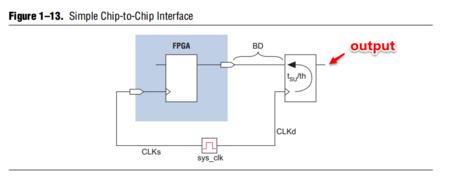

Figure 1–13

展示了一个典型的chip-to-chip输出接口,以及为了指定一个输出延时必要的各种参数。

Example 1–15 shows the constraints for system synchronous output

Example 1–15. System Synchronous Output Constraints

#specify the maximum external clock delay to the FPGA

set CLKs_max 0 .200

#specify the minimum external clock delay to the FPGA

set CLKs_min 0 .100

#specify the maximum external clock delay to the external device

set CLKd_max 0 .200

#specify the minimum external clock delay to the external device

set CLKd_min 0 .100

#specify the maximum setup time of the external device

set tSU 0 .125

#specify the minimum setup time of the external device

set tH 0 .100

#specify the maximum board delay

set BD_max 0 .180

#specify the minimum board delay

set BD_min 0 .120

#create a clock 10ns

create_clock -period 10 -name sys_clk [get_ports sys_clk]

#create the associated virtual input clock

create_clock -period 10 -name virt_sys_clk

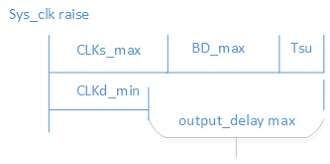

#create the output maximum delay for the data output from the FPGA that

#accounts for all delays specified

set_output_delay -clock virt_sys_clk \

-max [expr $CLKs_max + $BD_max + $tSU - $CLKd_min] \

[get_ports {data_in}]

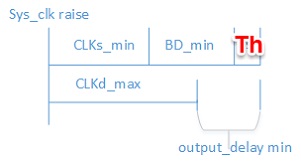

#create the output minimum delay for the data output from the FPGA that

#accounts for all delays specified

set_output_delay -clock virt_sys_clk \

-min [expr $CLKs_min + $BD_min - $tH - $CLKd_max] \

[get_ports {data_in}]

P21

如果想要了解更多关于约束 源同步输入输出(source synchronous input and output)接口,请查询

AN 433: Constraining and Analyzing Source-Synchronous Interfaces.

I/O Timing Requirements tSU, tH, and tCO

这部分描述的约束命令是 set_input_delay 和 set_output_delay

Example 1–16

展示了如何指定tsu和tH,通过用set_input_delay ,以及如何指定Tco,通过使用set_output_delay。Figure 1–14展示了一个在指定时序约束下的FPGA diagram

Example 1–16 shows the constraints for tSU, tH, and tCO.

Example 1–16. tSU, tH, and tCO Constraints

#Specify the clock period

set period 10 . 000

#Specify the required tSU

set tSU 1 . 250

#Specify the required tH

set tH 0 . 750

#Specify the required tCO

set tCO 0 . 4

#create a clock 10ns

create_clock -period $period - name clk [get_ports sys_clk ]

#create the associated virtual input clock

create_clock -period $period - name virt_clk

set_input_delay -clock virt_clk \

-max [ expr $period - $tSU] \

[get_ports {data_in }]

set_input_delay -clock virt_clk \

- min $tH \

[ get_ports {data_in }]

set_output_delay -clock virt_clk \

- max [ expr $period - $tCO] \(Note:这里不是很明白为什么这样计算)

[ get_ports {data_out }]

/4

/4

文章评论(0条评论)

登录后参与讨论